#### **Sequential Logic** Introduction to Computer Systems, Fall 2024 **Instructors**: Joel Ramirez Travis McGaha Head TAs: **Daniel Gearhardt** Adam Gorka Emily Shen Ash Fujiyama TAs: Ahmed Abdellah Ethan Weisberg Maya Huizar Meghana Vasireddy Garrett O'Malley Kirsch Angie Cao Hassan Rizwan Perrie Quek August Fu Caroline Begg lain Li Sidharth Roy Cathy Cao Sydnie-Shea Cohen Jerry Wang Claire Lu Juan Lopez Vivi Li Keith Mathe Yousef AlRabiah Eric Sungwon Lee

pollev.com/cis2400

How are you? Any Questions?

#### Logistics

- \* There was *no check-in* due today.

- \* HW05 due @ 11:59 pm on Fri, Oct 11

- Reminder; only 72 Hour extensions possible

# **Lecture Outline**

- Sequential Setup

- R-S Latch

- D Latch & Clock

- ✤ D Flip Flops

# So Far: Combinational Logic

- Always gives the same output for a given set of inputs

- State-less (i.e., no state or memory)

- What if I wanted to create something that depended on previous inputs/outputs/other state?

# So Far: Combinational Logic

- Always gives the same output for a given set of inputs

- State-less (i.e., no state or memory)

- What if I wanted to create something that depended on previous inputs/outputs/other state?

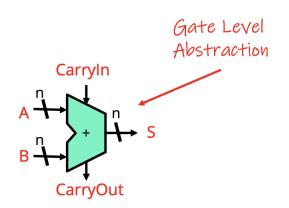

what if I wanted to increment the value S later?

Using current methods; we have no way of doing so.

We need to do something different!

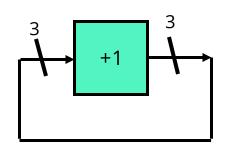

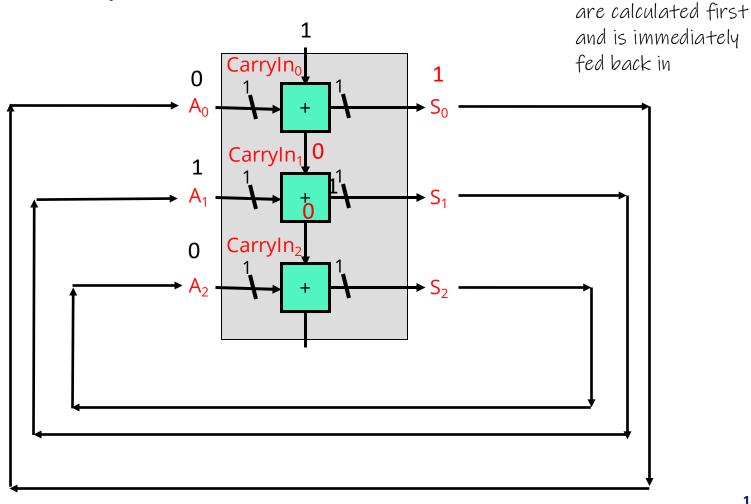

- What if we wanted to make a circuit that just continuously incremented an unsigned 3-bit integer *immediately*?

- We can make this with our usual incrementor

- What's the Expected Behavior?

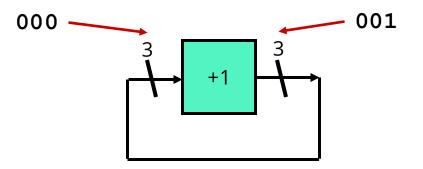

- What if we wanted to make a circuit that just continuously incremented an unsigned 3-bit integer *immediately*?

- We can make this with our usual incrementor

- What's the Expected Behavior?

# Doll Everywhere

pollev.com/cis2400

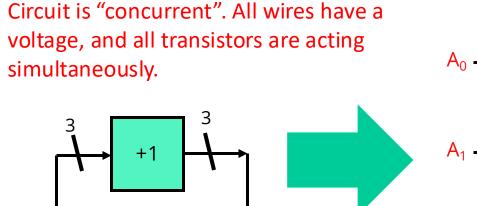

- Does the following counter circuit "work" like expected? Will it continuously count up till it overflows and starts at 0 again?

- A. Yes

- B. No

C. I'm not sure

pollev.com/cis2400

Does the following counter circuit "work" like expected?

Answer: Depends on how you look at it

A. Yes

- B. No

- C. I'm not sure

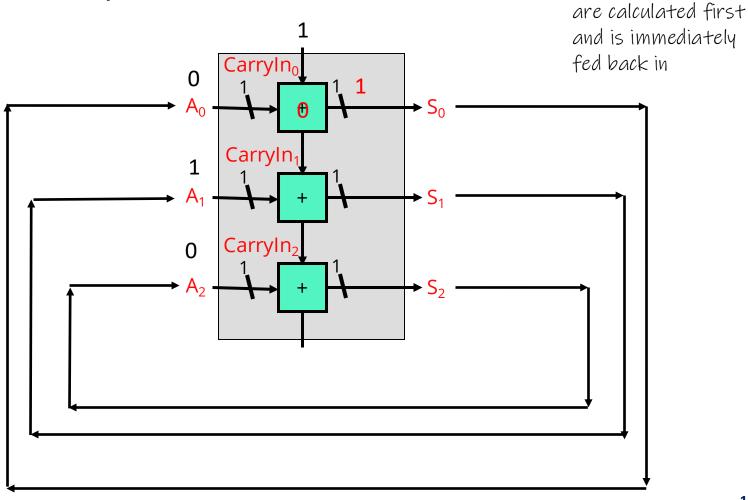

If we interpret the circuit "purely logical", it does count up, but each value is instantly replaced by the next. We'll assume the bits are immediately replaced by the output.

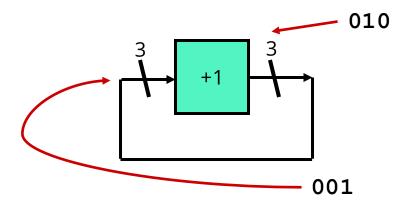

If we consider it as a physical circuit with gate delays...

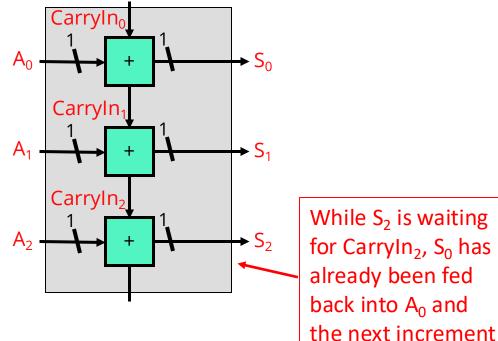

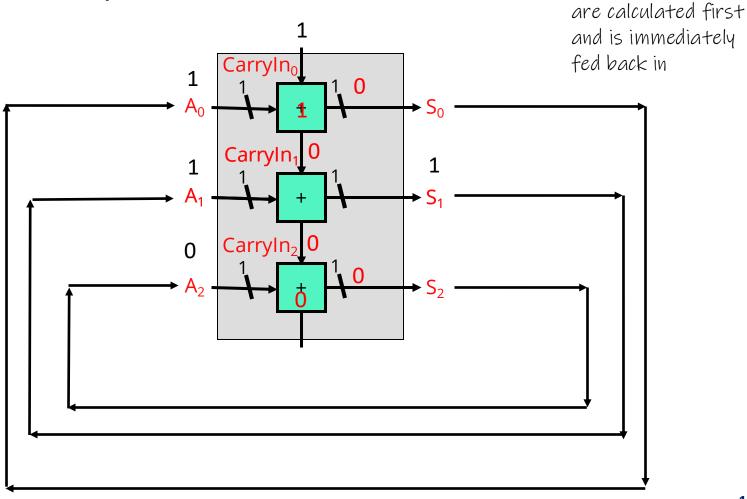

If we interpret the counter circuit as physical hardware with gate delay: Each bit output depends on the carry in from the previous bits

Due to gate delay, the correct output is not calculated before the next increment operation

has already begun

If we interpret the counter circuit as physical hardware with gate delay:

S<sub>0</sub> and CarryIn<sub>1</sub>

If we interpret the counter circuit as physical hardware with gate delay:

S<sub>0</sub> and CarryIn<sub>1</sub>

If we interpret the counter circuit as physical hardware with gate delay: S<sub>0</sub> and CarryIn<sub>1</sub>

# **Combinational Counter Review**

- This example was just here to highlight why we need sequential circuits:

- to be able to store state

- to synchronize our circuits

This lecture will be about setting up how we use gates to store state (data) and synchronize (time) signals.

# **Lecture Outline**

- Sequential Setup

- R-S Latch

- D Latch & Clock

- ✤ D Flip Flops

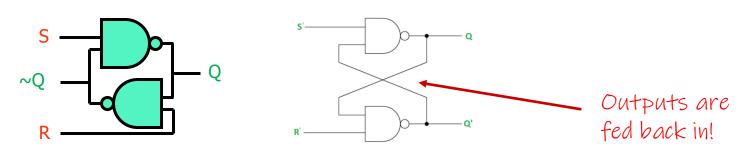

#### S-R Latch

- Can store a bit value depending on its inputs

- called a "Latch" because it can "Latch" onto data coming in

- Is a Bi-stable circuit: Can exist happily in two stable states

You can push the latch from one state to another by <u>s</u>etting or <u>r</u>esetting it with S-R signals

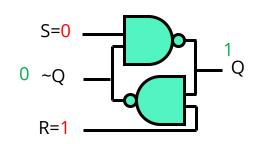

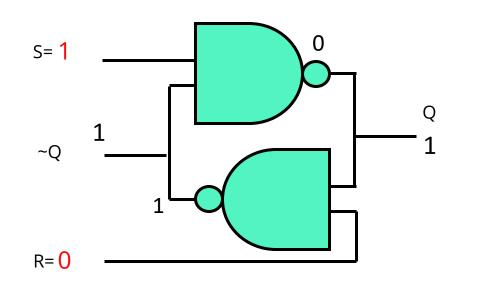

# **S-R Latch Implementation**

- Can be implemented by cross coupled NAND gates

- Two inputs: S (SET) & R (RESET)

- Two outputs: Q and NOT(Q)

- Notation: NOT(Q) =  $\sim Q = Q' = \overline{Q}$

Another common way of drawing the same circuit

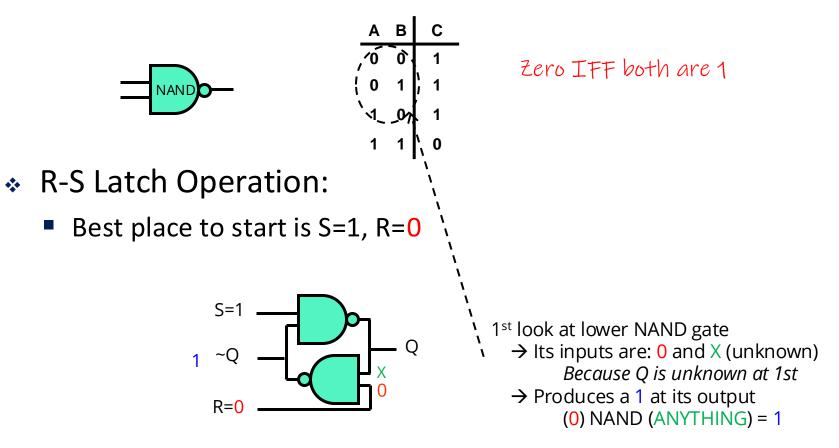

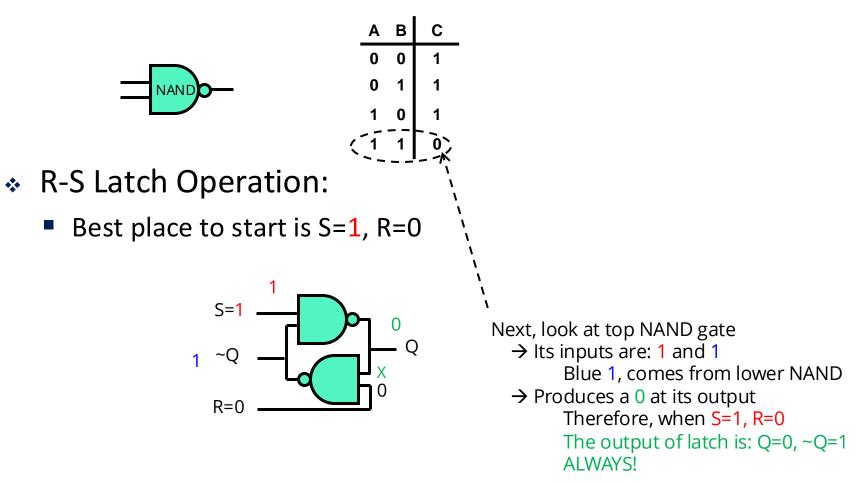

First, recall truth table for a NAND gate:

First, recall truth table for a NAND gate:

First, recall truth table for a NAND gate:

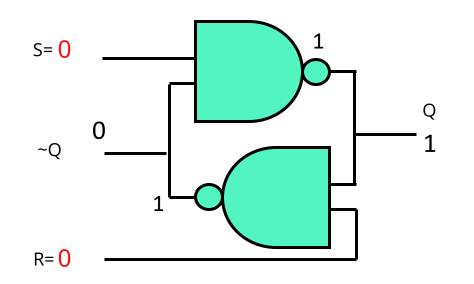

R-S Latch Operation:

NAND

Truth Table for R-S Latch:

| ACTION | S | R | Q | ~Q |

|--------|---|---|---|----|

|        | 0 | 0 |   |    |

|        | 0 | 1 |   |    |

| RESET  | 1 | 0 | 0 | 1  |

|        | 1 | 1 |   |    |

Called the "**RESET**" **action**, Q is "reset" to 0 Also, notice: Q and ~Q opposite

First, recall truth table for a NAND gate:

First, recall truth table for a NAND gate:

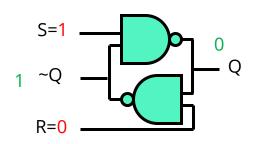

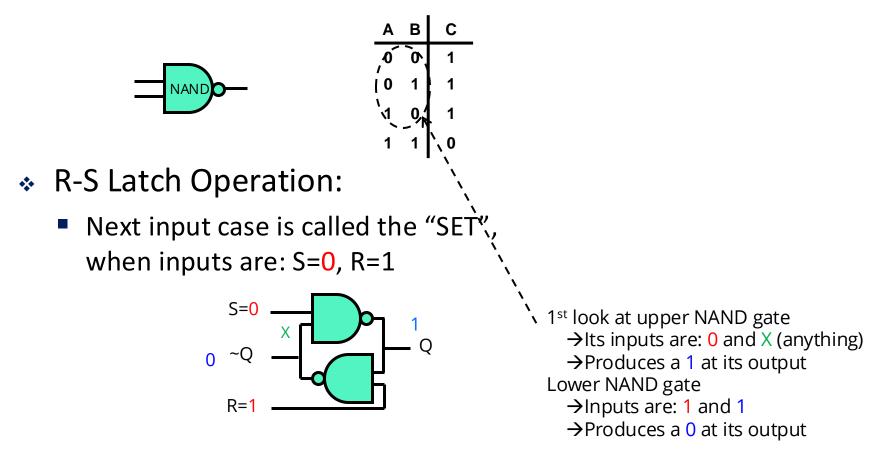

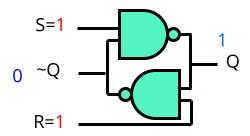

R-S Latch Operation:

Truth Table for R-S Latch:

| ACTION | S | R | Q | ~Q |

|--------|---|---|---|----|

|        | 0 | 0 |   |    |

| SET    | 0 | 1 | 1 | 0  |

| RESET  | 1 | 0 | 0 | 1  |

|        | 1 | 1 |   |    |

**SETs** LATCH to have a "1" at the output

First, recall truth table for a NAND gate:

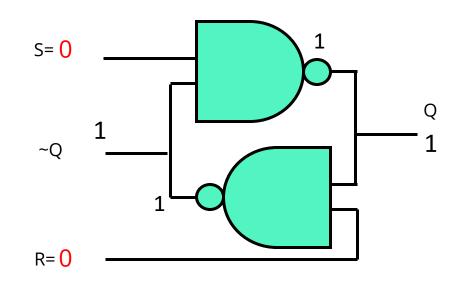

R-S Latch Operation:

NAND

- Last valid input case is the "HOLD" S=1, R=1

- If we have just "SET" Latch, we will have Q=1, ~Q=0 already

Upper NAND gate

- $\rightarrow$  Has S=1 & former value of ~Q=0

- → Produces a 1 at its output (same Q as when it started)

Lower NAND gate

- $\rightarrow$  Inputs are: 1 and 1

- $\rightarrow$  Produces a 0 at its output (same ~Q)

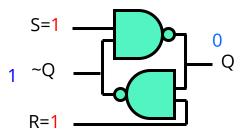

First, recall truth table for a NAND gate:

R-S Latch Operation:

NAND

- Last valid input case is the "HOLD" S=1, R=1

- If we have just "RESET" Latch, we will have Q=0, ~Q=1 already

Upper NAND gate → Has S=1 & value of ~Q=1

→ Produces a 0 at its output (same Q as when it started)

Lower NAND gate

- $\rightarrow$  Inputs are: 0 and 1

- $\rightarrow$  Produces a 1 at its output (same  $\sim Q$ )

В

0

1

0

A 0

0

1

1

С

1

1

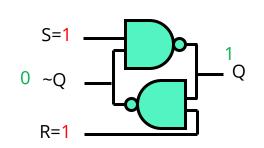

First, recall truth table for a NAND gate:

NAND

*Truth Table for R-S Latch:*

| ACTION | S | R | Q | ~Q  |

|--------|---|---|---|-----|

|        | 0 | 0 |   |     |

| SET    | 0 | 1 | 1 | 0   |

| RESET  | 1 | 0 | 0 |     |

| HOLD   | 1 | 1 | 1 | 0 🖌 |

| HOLD   | 1 | 1 | 0 | 1 🖌 |

THIS HOLD's the last value on its outputs!

- ✤ What happens with S=0 and R=0?

- Short answer: confusion

Q = 1 and  $\sim Q = 0$  are set before this

- ✤ What happens with S=0 and R=0?

- Short answer: confusion

Q = 1 and  $\sim Q = 0$  are set before this

- ✤ What happens with S=0 and R=0?

- Short answer: confusion

- Real circuits depend on both Q and ~Q

- Strange things may happen if both are 1

Truth Table for R-S Latch:

| ACTION  | S | R | Q | ~Q  |

|---------|---|---|---|-----|

| ILLEGAL | 0 | 0 | 1 | 1   |

| SET     | 0 | 1 | 1 | 0 🔨 |

| RESET   | 1 | 0 | 0 |     |

| HOLD    | 1 | 1 | 1 | 0 🖌 |

| HOLD    | 1 | 1 | 0 | 1 K |

#### CIS 2400, Fall 2024

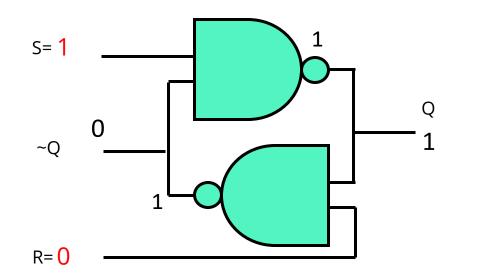

# Analyzing the Operation of a Latch

- What "really" happens with S=1 and R=0?

- Let's see.

Q = 1 and  $\sim$ Q = 0 are set before this

Wait? There both 1? I thought that only happened in the illegal state?

Well, let's continue to hold the signal for another round.

- ✤ What happens with S=1 and R=0?

- Let's see.

Q = 1 and  $\sim Q = 0$  are set before this

Ahh, so it 'stabilizes' into the Reset State!

Yup, that's right.

For now, we'll ignore this when we Set or Reset...

Just want to show you how finicky these really are.

# **Lecture Outline**

- Sequential Setup

- R-S Latch

- D Latch & Clock

- ✤ D Flip Flops

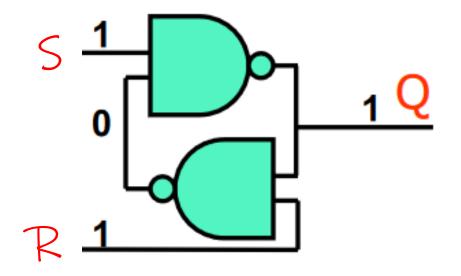

Goal: Make the RS latch more understandable

RS LATCH

#### Goal: Make the RS latch more understandable

To make it more understandable, we'll make it more complicated!

- Goal: Make the RS latch more understandable

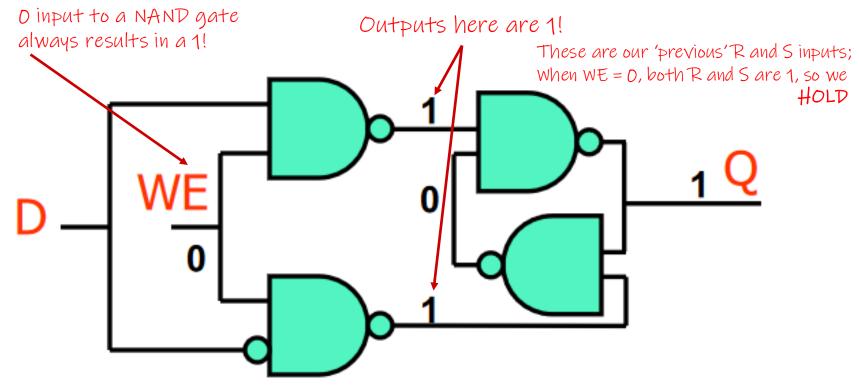

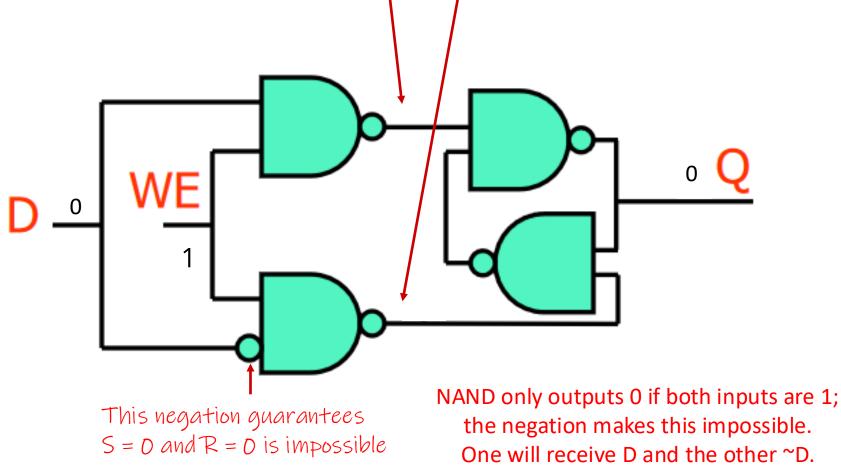

- Replace R and S with D, add WE for utility

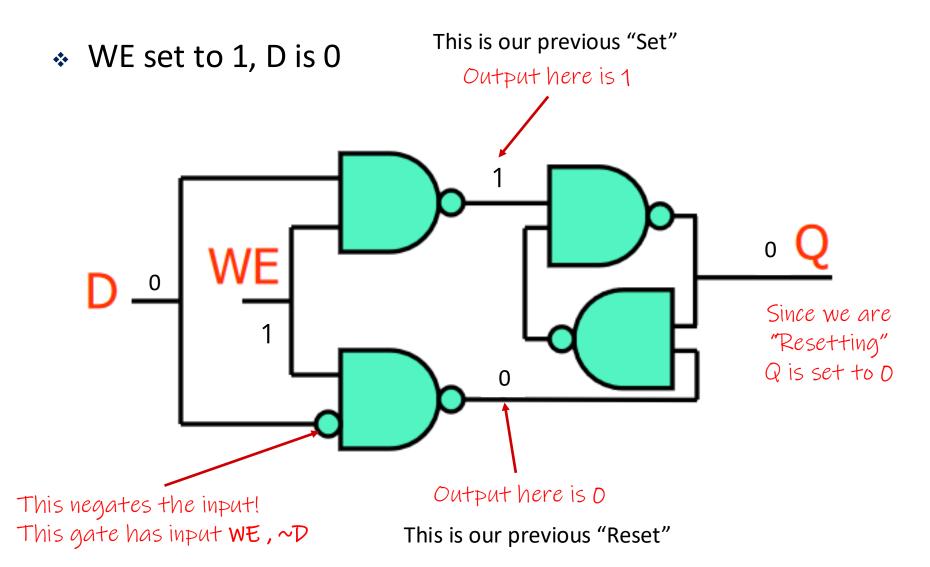

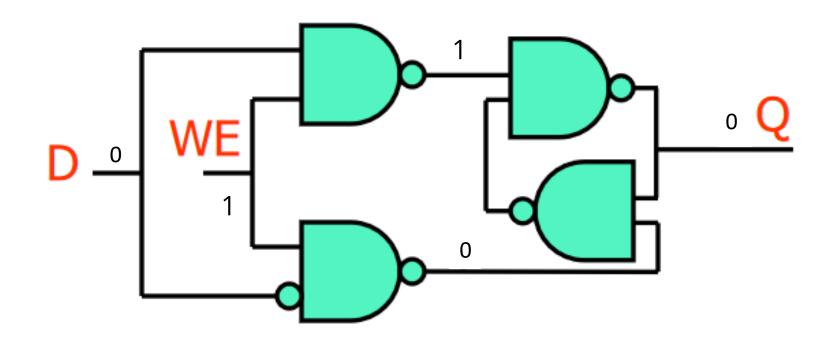

- D the data we want to store (either 1 or 0)

- ✤ WE, whether writing (storing that bit) is enabled.

- If not enabled, Q (the stored data) maintains current value

- If enabled, then Q is set to be D

- Impossible for S=0 and R = 0 case to occur

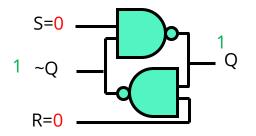

#### ✤ WE set to 0, D is unknown

### **D** Latch

### **D** Latch

WE set to 1, D is 0

In D Latch terms, **Q** is equal to the value of **D** when WE is **1**

### **D** Latch

• Why is it impossible for S = 0 & R = 0?

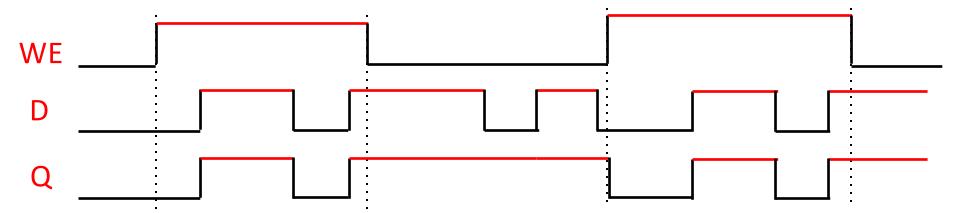

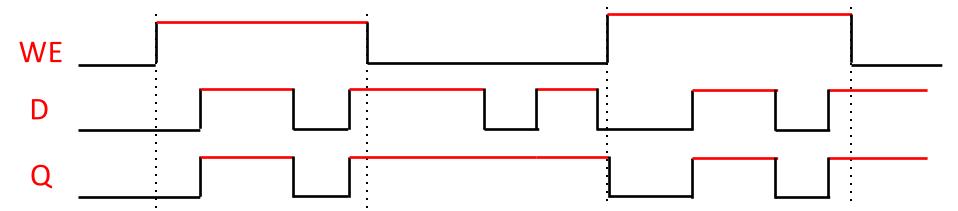

# **Timing Diagrams**

- Diagram to represent how signals change over time

- ✤ WE: Write Enable Signal

- WE is <u>high</u>: the latch is <u>open</u> and Q is the same as D.

- WE is <u>low</u>: the latch is <u>closed</u> and Q stays the same. "Holds"

- The input signal should be stable a certain amount of time before the WE signal is lowered for proper operation. This is referred to as the <u>setup time</u>.

# **Timing Diagrams**

# Poll Everywhere

pollev.com/cis2400

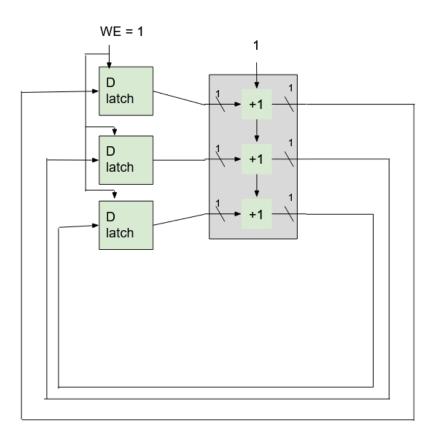

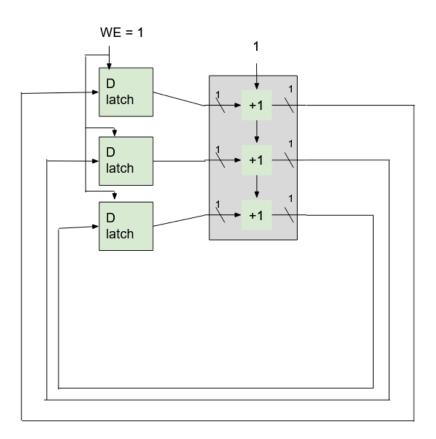

- Does the following counter circuit "work" better than the previous counter circuit? Assume WE is hard-coded as 1.

- A. Yes

- B. No

- C. I'm not sure

# Doll Everywhere

pollev.com/cis2400

Does the following counter circuit "work" better than the previous counter circuit? Assume WE is hard-coded as 1.

A. Yes B. No

C. I'm not sure

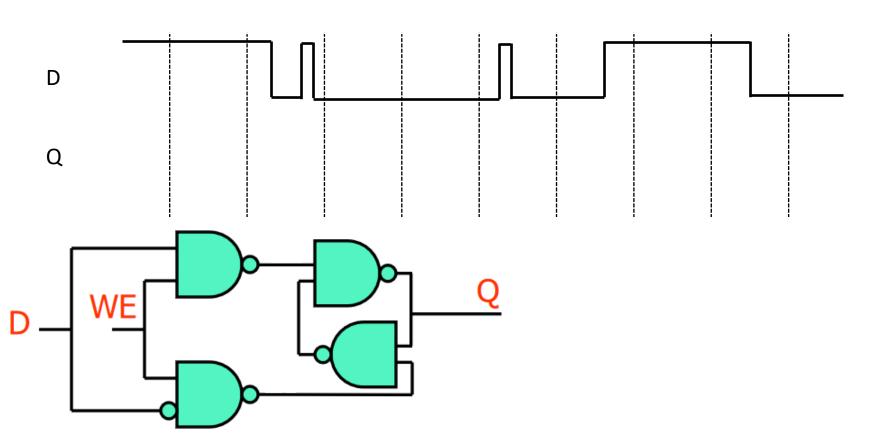

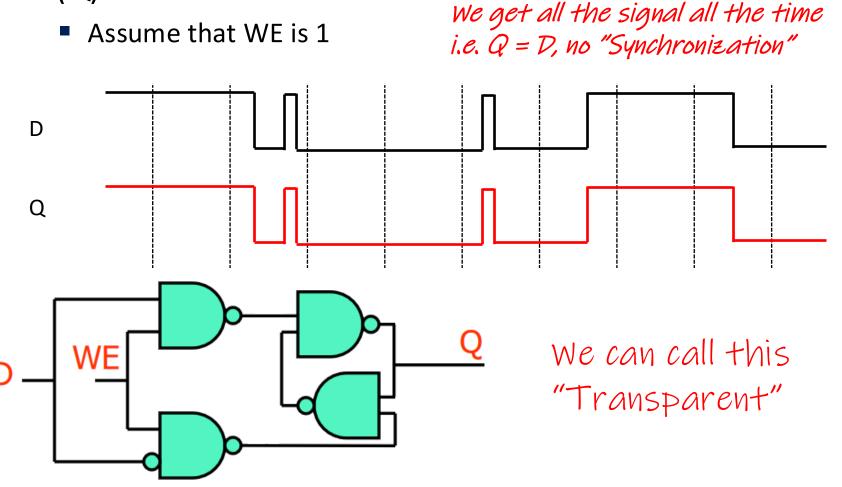

#### Transparency

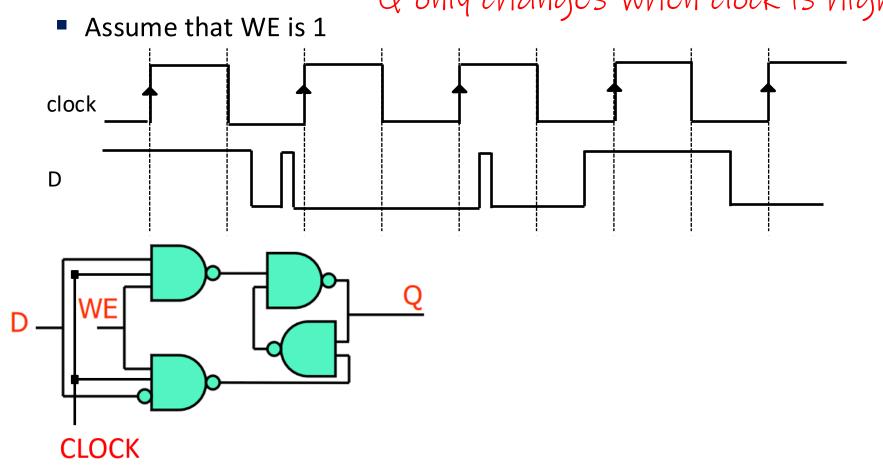

- Consider the following signal. What is the signal output

(Q) of our D Latch?

- Assume that WE is 1

#### Transparency

Consider the following signal. What is the signal output

(Q) of our D Latch?

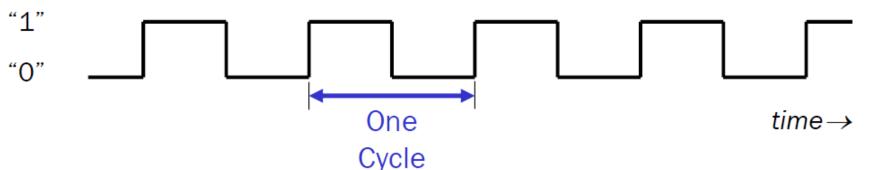

# **The Clock**

- A regular up & down signal which can be used for timing & synchronization.

- Is the "heartbeat" of our system.

- Sort of like a metronome

- Clock Period = Duration of one clock cycle

- Clock Frequency = 1/Period

- Typical frequency: 2.5GHz = 2.5e9 Hz

- Typical period: 0.4 nanoseconds

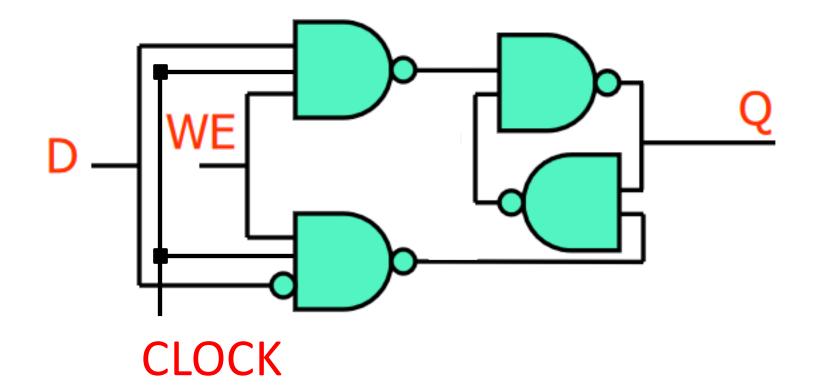

# **D** Latch with Clock

- Clock could be included into our D-Latch

- This affects out transparency (see next slide)

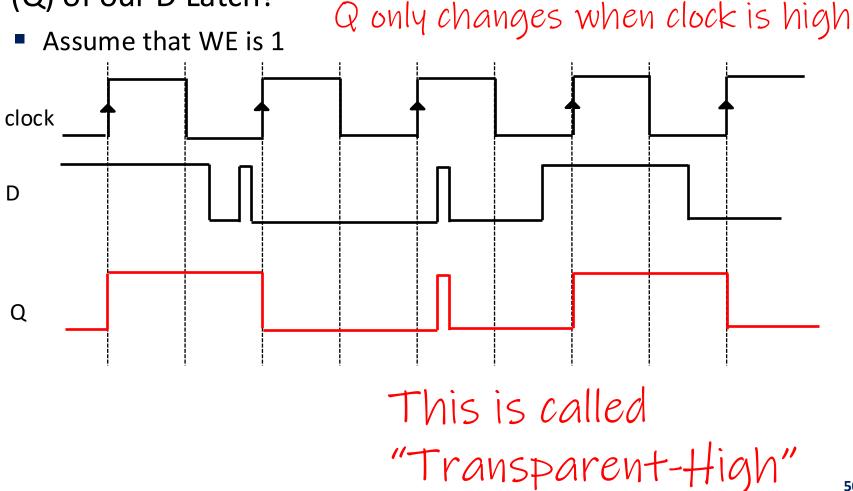

### **Transparency?**

Consider the following signal. What is the signal output

(Q) of our D Latch?

Q only changes when clock is high

### **Semi-Transparency**

Consider the following signal. What is the signal output

(Q) of our D Latch?

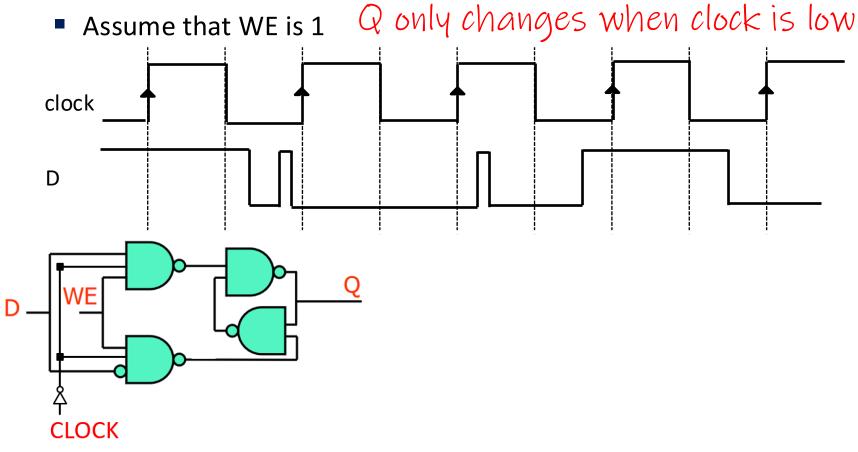

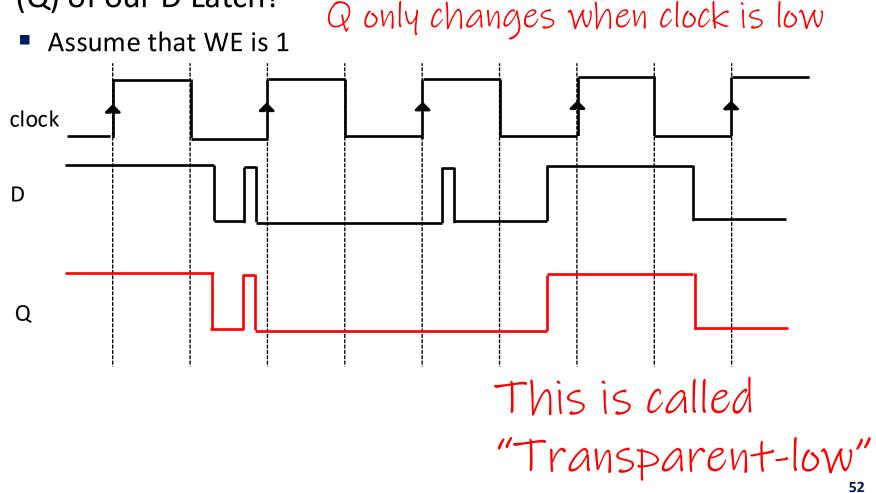

# **Semi-Transparency?**

Consider the following signal. What is the signal output

(Q) of our D Latch? (Note how the clock is inverted)

# **Semi-Transparency?**

Consider the following signal. What is the signal output (Q) of our D Latch?

# **Lecture Outline**

- Sequential Setup

- R-S Latch

- D Latch & Clock

- **\* D Flip Flops**

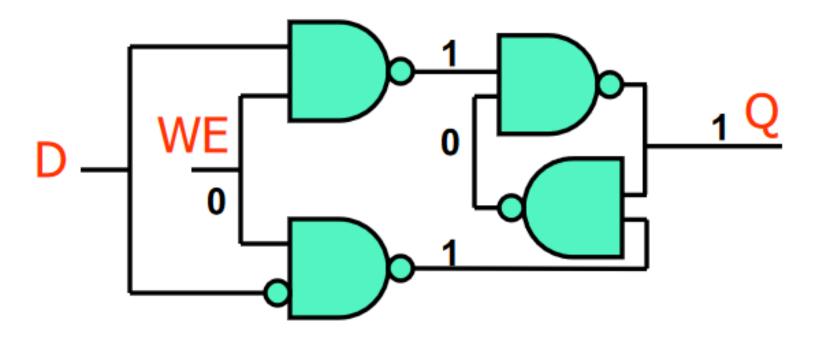

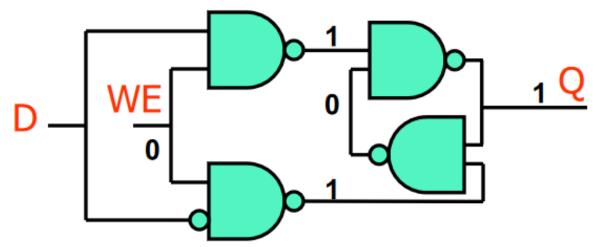

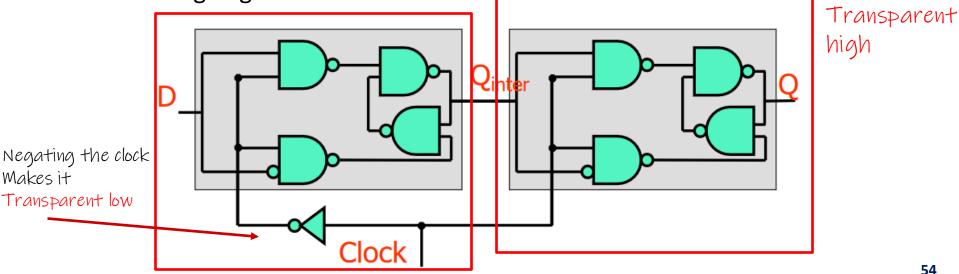

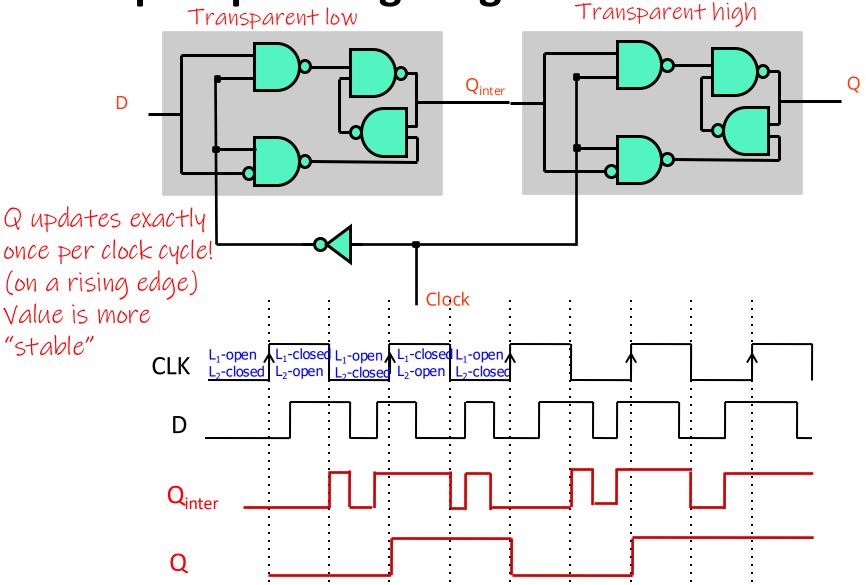

# **D** Flip Flop

- Made by:

- Appending a transparent-high onto a transparent-low latch

- Rules:

- Q<sub>inter</sub> is the result of passing D through a transparent-low latch

- Q is the result of passing Q<sub>inter</sub> through a transparent-high latch

- Effectively, this makes Q only "sensitive" to the signal value at the rising edge of the clock

# **D Flip Flop Timing Diagram**

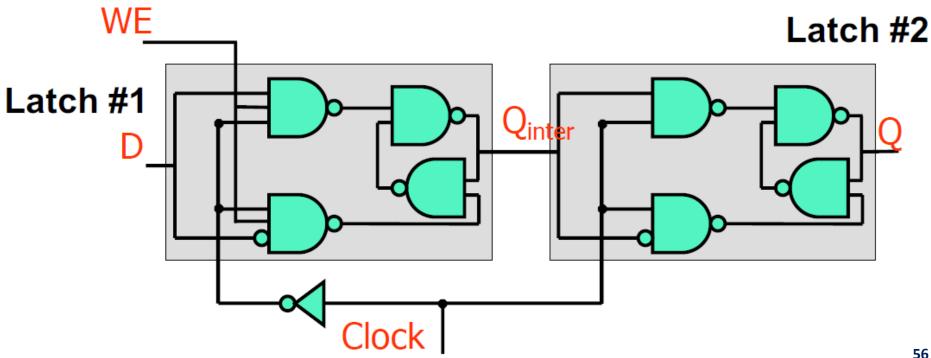

# Flip Flop with WE

- Can attach WE to the first latch to enable WE for the flipflop.

- When WE is low, latch #1 is closed and Q<sub>inter</sub> cannot change. Q will become Q<sub>inter</sub> if not already.

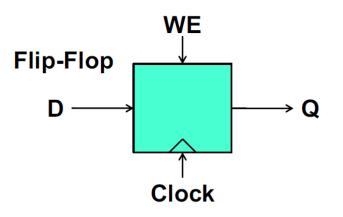

# **Flip Flops Summary**

- We can abstract away the details of a Flip Flop as a 1-bit storage container.

- Takes in an input D

- Has an output or stored value "Q"

- Takes a clock input (often represented with a triangle)

- Usually has a WE to control if it will update on the next rising edge

- A set of D flip flops can be grouped together to form a register (storage for a multiple-bit value, more on this next lecture)

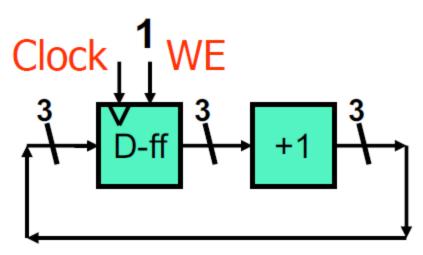

### **Working Counter**

Use a clocked 3-bit register (storage) made of D flip-flops

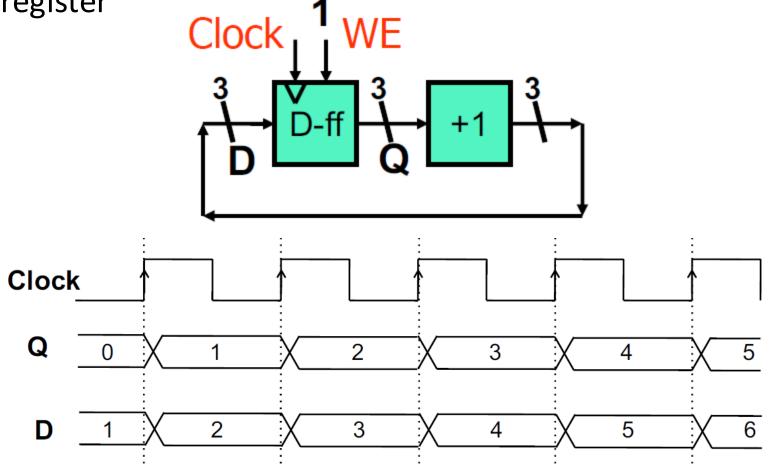

### **Counter Timing Diagram**

Incrementor computes input +1, the next value of the register

### **Next Lecture**

- Memory

- What really is it and how is it accessed?

- Registers

- More Clock!