ESE3700: Circuit-Level Modeling, Design, and Optimization for Digital Systems

Lec 6: February 10, 2025 MOS Transistor Operating Regions Part 2, Parasitics

- Operating Regions

- Resistive

- Saturation

- Subthreshold

- Velocity Saturation

- Short Channel Effects

- V<sub>th</sub>

- Drain Induced Barrier Lowering

- Capacitance

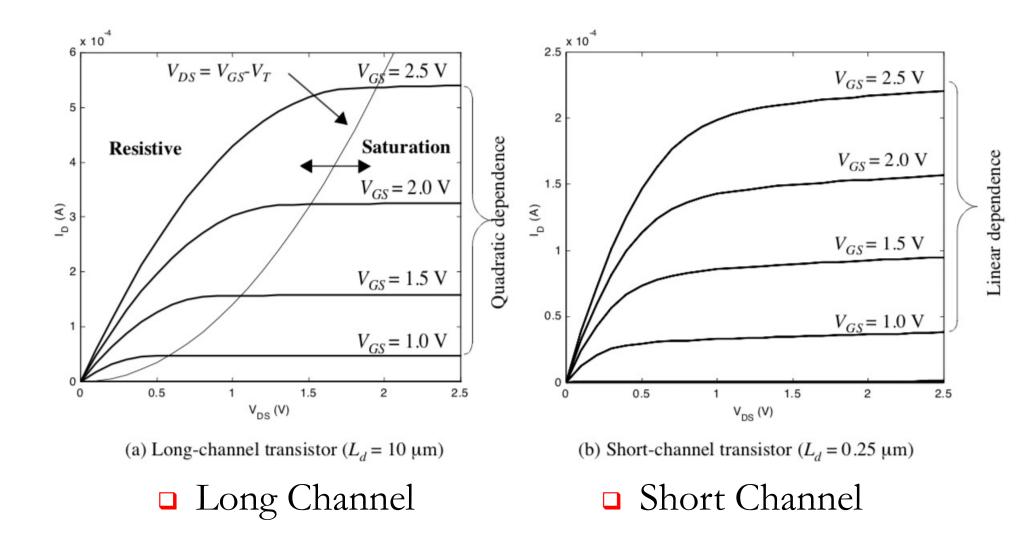

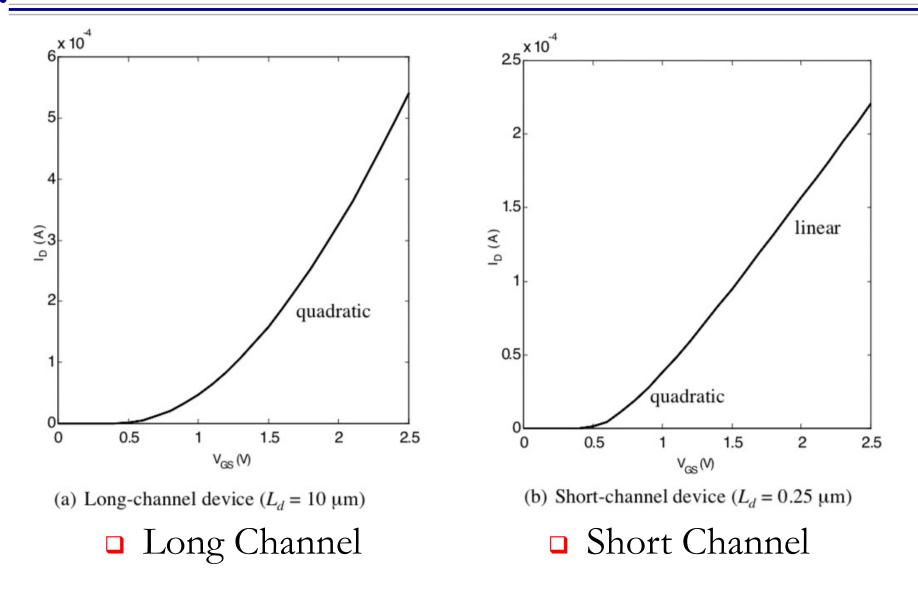

### Velocity Saturation

- Model assumes carrier velocity increases with field

- Increases with voltage proportionally to mobility

$$v = \mu_n \cdot \frac{V_{DS}}{L_{eff}} = \left(\frac{\mu_n}{L_{eff}}\right) V_{DS}$$

Model assumes carrier velocity increases with field

Increases with voltage proportionally to mobility

$$v = \mu_n \cdot \frac{V_{DS}}{L_{eff}} = \left(\frac{\mu_n}{L_{eff}}\right) V_{DS}$$

#### □ (a) What is the electrical field in the channel?

$$L_{eff} = 25nm, V_{DS} = 1V$$

Uniform Field =  $\frac{V_{DS}}{L_{eff}}$

□ Velocity:

$v = F \cdot \mu_n$

- Electron mobility:  $\mu_n = 500 cm^2 / (V \cdot s)$

- □ (b) What is the electron velocity?

$$I = \left(\frac{1}{R}\right)V$$

I increases

linearly in V

□ What's I?

$$I = \left(\frac{1}{R}\right)V$$

- I increases

linearly in V

- □ What's I?

- $\Delta Q/\Delta t$

- Speed at which charge moves

$$I = \left(\frac{1}{R}\right)V$$

$$Field = \frac{V_{DS}}{L_{eff}}, v = \mu_n \cdot F$$

$$v = \mu_n \cdot \frac{V_{DS}}{L_{eff}} = \left(\frac{\mu_n}{L_{eff}}\right) V_{DS}$$

I increases

linearly in V

Velocity increases linearly in V

- □ What's I?

- $\Delta Q/\Delta t$

- Speed at which charge moves

- What's a moving electron?

Electric Field E<sub>v</sub> (V/cm)

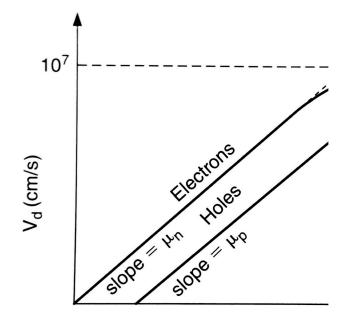

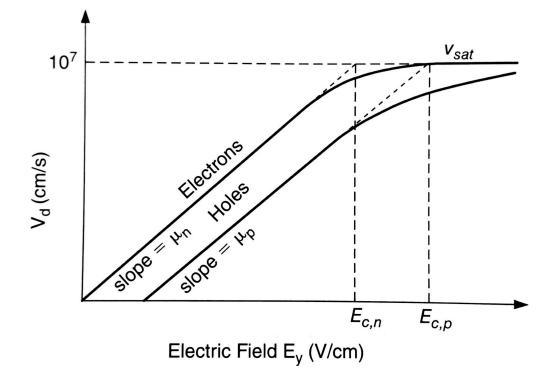

□ Velocity –

increases for increasing field with slope of mobility

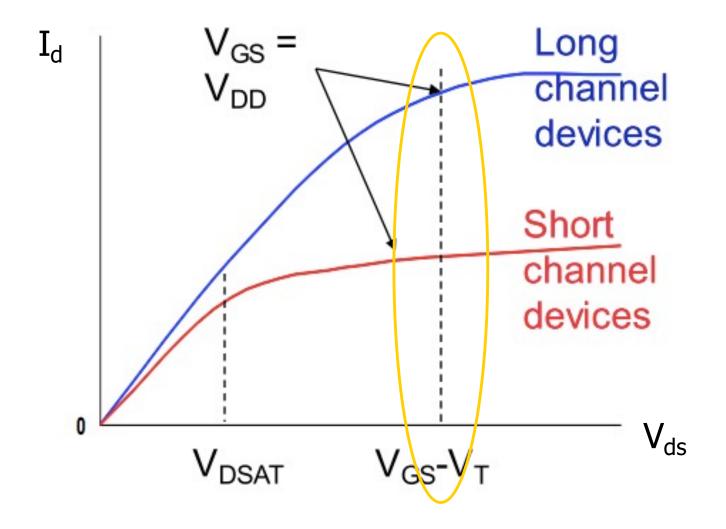

#### Velocity –

- increases for increasing field with slope of mobility

- saturates for increasing field

- More likely to hit the critical field in short channel

- Model assumes carrier velocity increases with field

- Increases with voltage proportionally to mobility

- □ There is a limit to how fast carriers can move

- Limited by scattering effects

- $\sim 10^5 \mathrm{m/s}$

- □ Encounter *velocity saturation* when channel short

- Modern processes, L is short enough to reach this region of operation

# Velocity Saturation (Preclass 1)

- (c) At what voltage do we hit the speed limit 10<sup>5</sup>m/s?

- $L_{eff}=25nm, V_{ds}=1V$

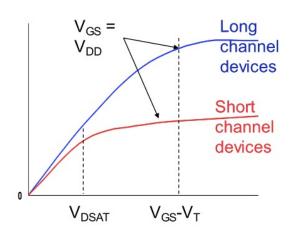

- $V_{DSAT}$  = voltage at which velocity (current) saturates

$$I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left(V_{GS} - V_{th}\right) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

• Once velocity saturates:

$$I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

• Once velocity saturates:

$$V_{DS} = V_{DSAT} \Longrightarrow I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left(V_{GS} - V_{th}\right) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right]$$

$$I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

• Once velocity saturates:

$$V_{DS} = V_{DSAT} \Rightarrow I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left(V_{GS} - V_{th}\right) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right]$$

$$I_{DS} = \left(\mu_n \frac{V_{DSAT}}{L}\right) C_{OX} W \left[ \left(V_{GS} - V_{th}\right) - \frac{V_{DSAT}}{2} \right]$$

$$I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

• Once velocity saturates:

$$V_{DS} = V_{DSAT} \Rightarrow I_{DS} = \mu_n C_{OX} \left(\frac{W}{L}\right) \left[ \left(V_{GS} - V_{th}\right) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right]$$

$$I_{DS} = \left(\mu_n \frac{V_{DSAT}}{L}\right) C_{OX} W \left[ \left(V_{GS} - V_{th}\right) - \frac{V_{DSAT}}{2} \right]$$

$$I_{DS} \approx v_{sat} C_{OX} W \left[ \left(V_{GS} - V_{th}\right) - \frac{V_{DSAT}}{2} \right]$$

- Once velocity saturates we can still increase current with parallelism

- Effectively make a wider device

$$I_{DS} \approx v_{sat} C_{OX} W \left[ \left( V_{GS} - V_{th} \right) - \frac{V_{DSAT}}{2} \right]$$

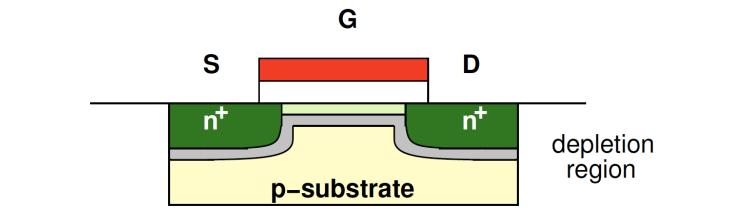

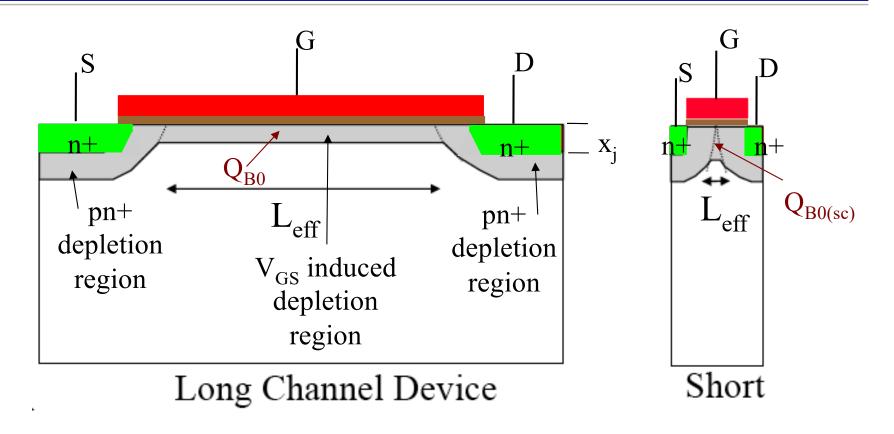

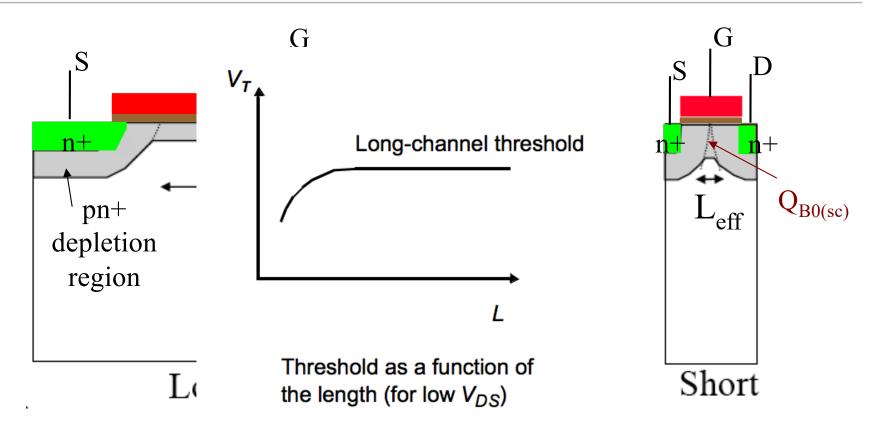

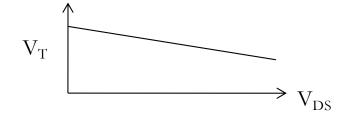

#### Threshold

Short Channel Effects –  $V_T$  Reduction

$V_{T0}$  (short channel) =  $V_{T0}$  -  $\Delta V_{T0}$

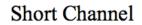

# Short Channel Effects – $V_T$ Reduction

$V_{T0}$  (short channel) =  $V_{T0}$  -  $\Delta V_{T0}$

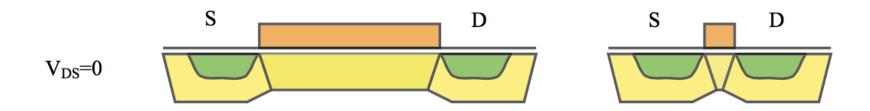

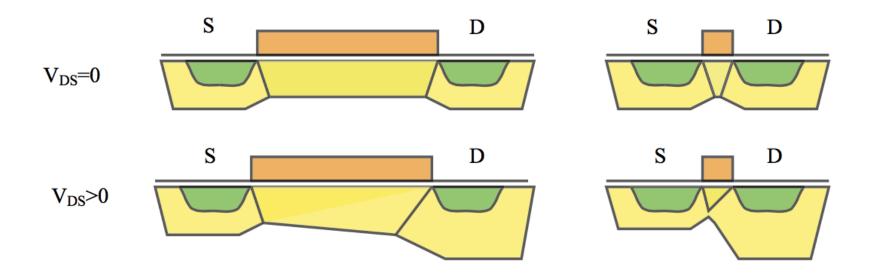

- Drain Induced Barrier Lowering

- $V_T$  Reduction with Drain Bias

Long Channel

Short Channel

- Drain Induced Barrier Lowering

- $V_T$  Reduction with Drain Bias

Long Channel

Short Channel

- Drain Induced Barrier Lowering

- $V_T$  Reduction with Drain Bias

## Threshold Reduction Impact

□ What does it impact most?

- Which device, has large V<sub>ds</sub>?

- How does this effect operation?

- Speed of switching?

- Leakage?

- Design a circuit to perform a function with specified minimum speed and optimized power (minimized with an upper bound)

- Zero order model to design topology

- First order model to meet speed spec

- Rise/fall times, propagation delay, gate capacitance, output stage equivalent resistance

- Transistor IV curves

- Iterative SPICE simulation tweak knobs to optimize for power (switching (dynamic), leakage (static), etc.)

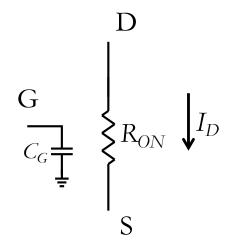

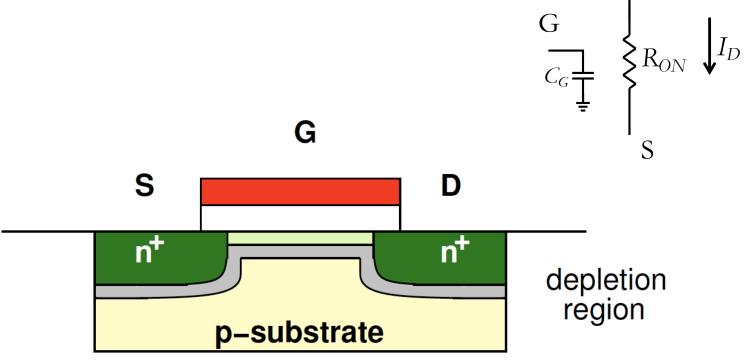

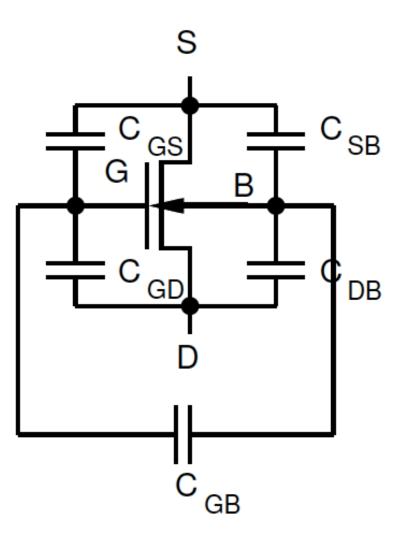

□ First order: gate input looks like a capacitor

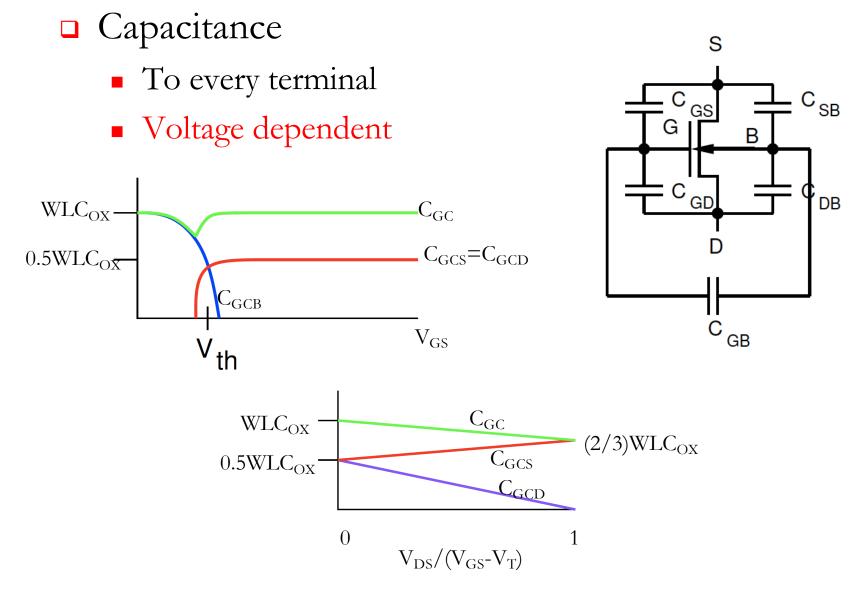

**D** Today:

- Capacitance is not constant

- Capacitance not physically to gnd

- Modeled as such

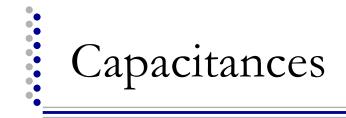

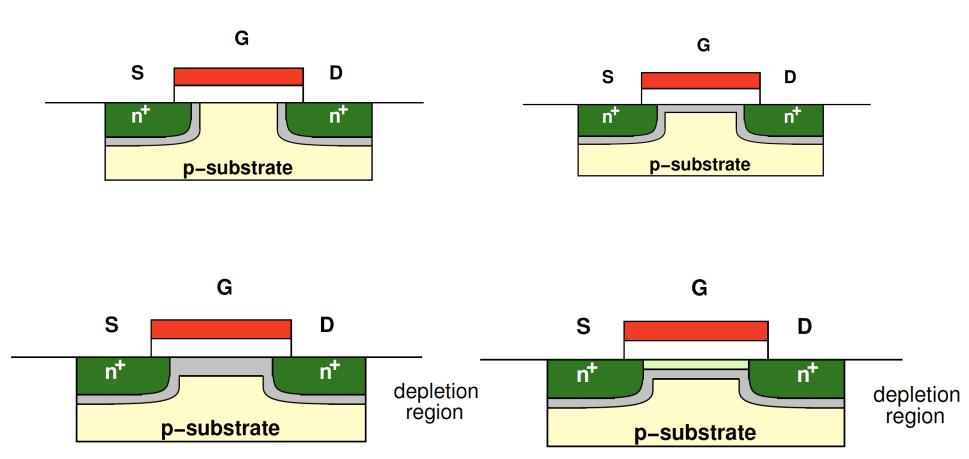

### Capacitance Setup

- Modeled gate with a capacitor to ground

- ... but ground isn't really one of our terminals

- Don't connect directly to it

- ...source and body are *often* at ground...

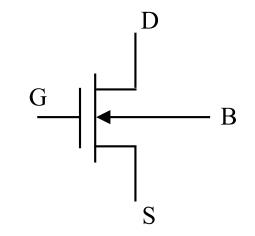

D

- Four Terminals

- □ How many combinations?

- 4 things taken 2 at a time?

Penn ESE3700 Spring 2023

В

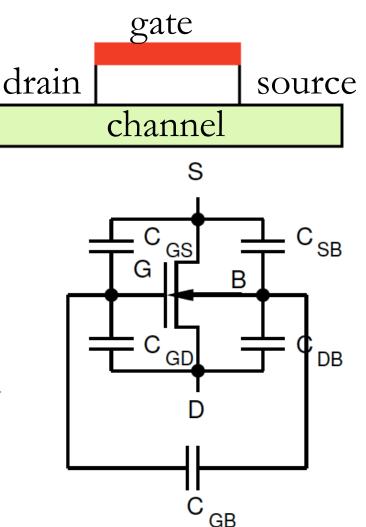

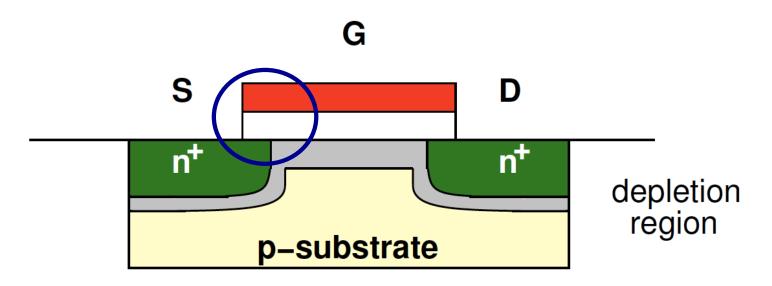

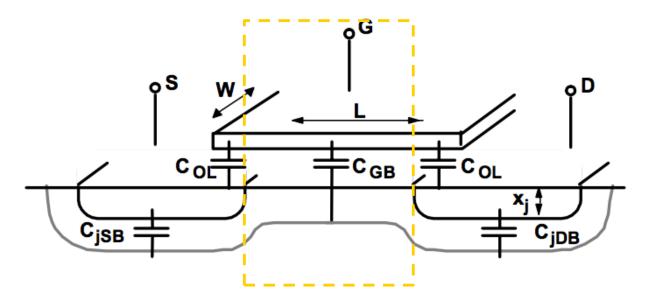

#### Capacitance Decomposition

- Any two conductors separated by an insulator form a parallel-plate capacitor

- **T**wo types

- Extrinsic Outside the box (e.g. junction, overlap)

- Intrinsic Inside the box (e.g. gate-to-channel)

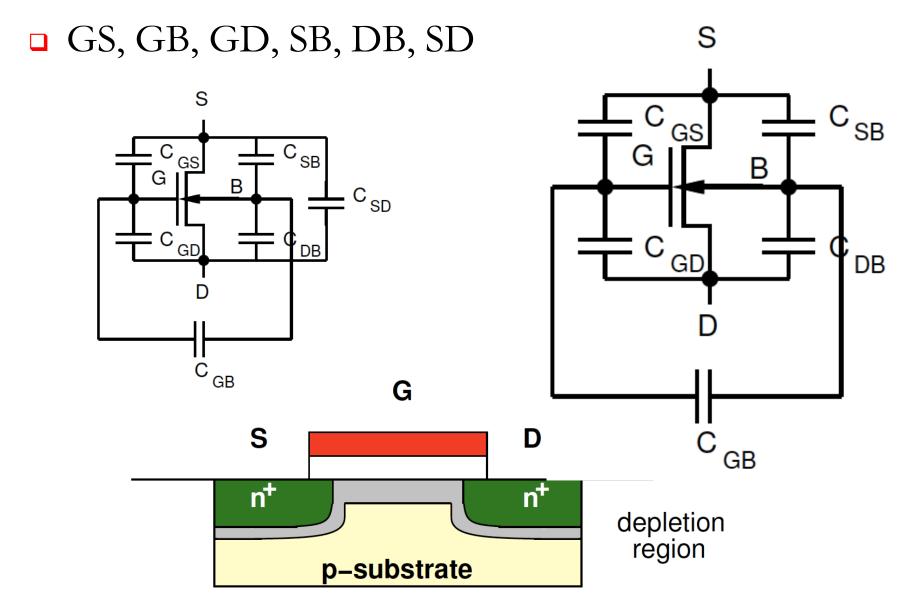

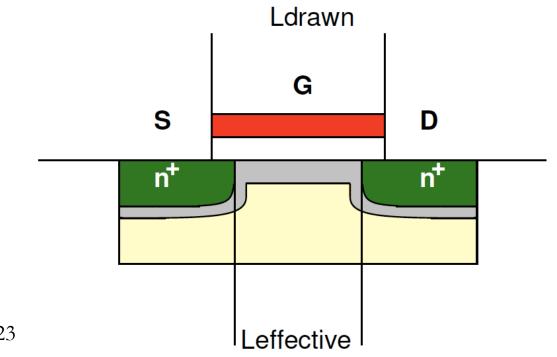

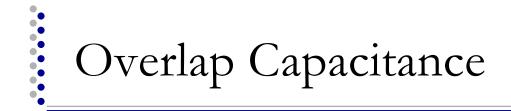

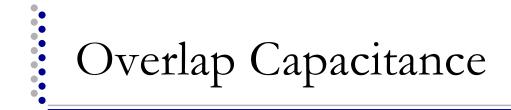

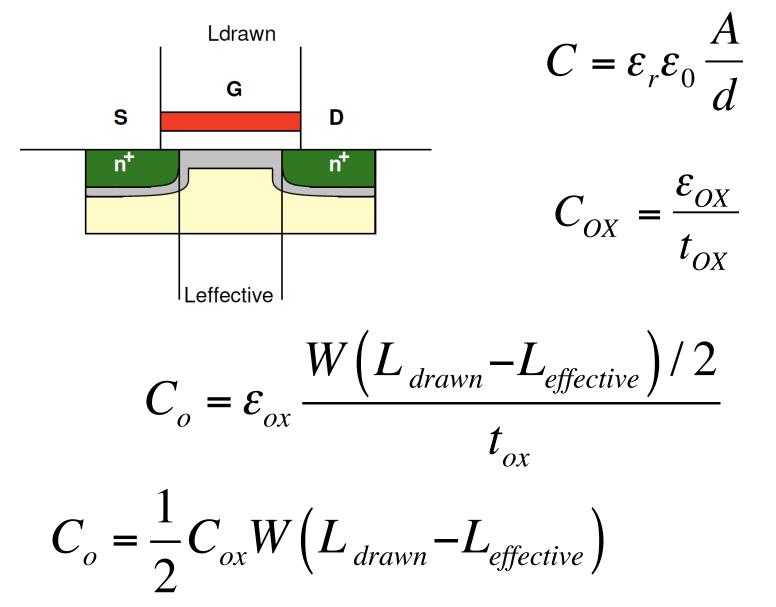

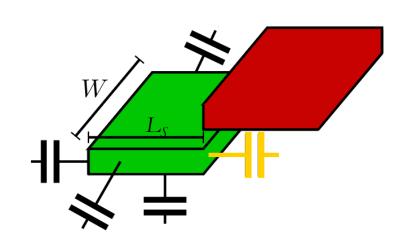

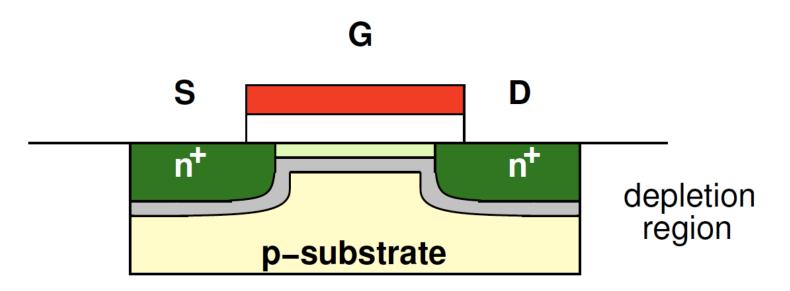

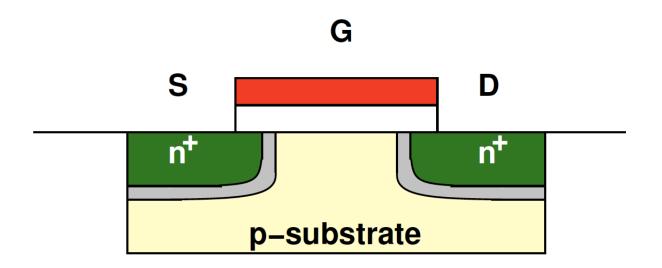

### Overlap Capacitance

What is the capacitive implication of gate/source and gate/drain overlap?

#### □ Length of overlap?

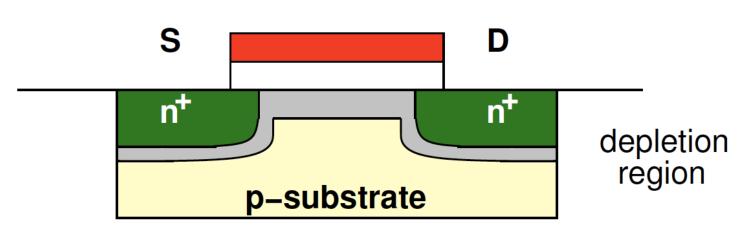

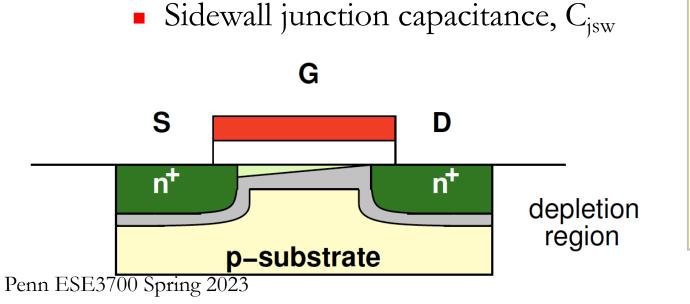

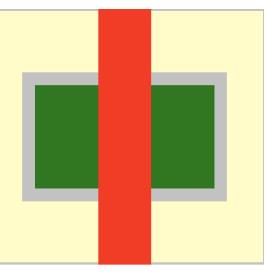

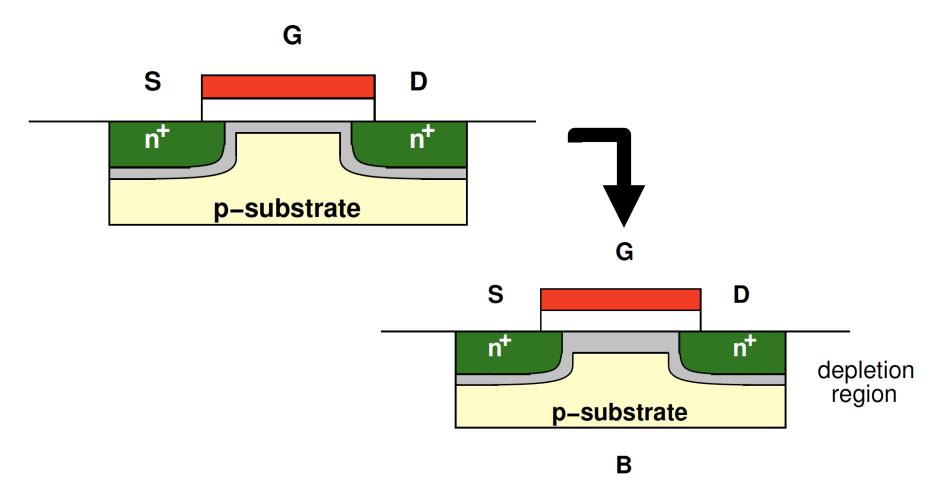

### Junction Capacitances

### Junction (diffusion) Capacitance

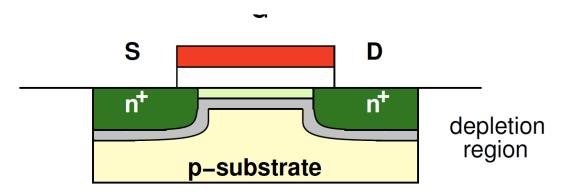

- $\square$  n<sup>+</sup> contacts are formed by doping = diffusion

- Depletion under diffusion region (bottom-plate)

- Due to reverse biased PN junction

- Bottom-plate junction capacitance, C<sub>j</sub>

- Depletion around perimeter (sidewall) of diffusion region

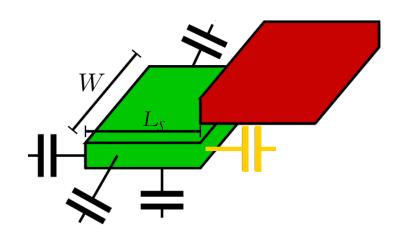

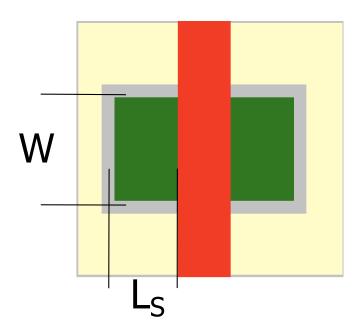

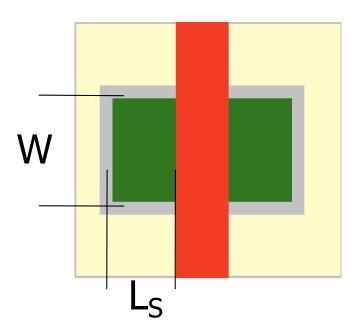

## Junction (Diffusion) Capacitance

- □  $C_j$  Bottom-plate junction capacitance (F/Area)

- $C_{jsw}$  Sidewall junction capacitance (F/Length)

- □  $L_S$  length of diffusion region

$$C_{diff} = C_j L_S W +$$

## Junction (Diffusion) Capacitance

- □  $C_j$  Bottom-plate junction capacitance (F/Area)

- □  $C_{jsw}$  Sidewall junction capacitance (F/Length)

- $\Box$  L<sub>S</sub> length of diffusion region

$C_{diff} = C_i L_S W + C_{isw} (2L_S + W)$

#### Gate-to-channel

- Any two conductors separated by an insulator form a parallel-plate capacitor

- **T**wo types

- Extrinsic Outside the box (e.g. junction, overlap)

- Intrinsic Inside the box (e.g. gate-to-channel)

# Gate-to-Bulk Capacitance

- Looks like parallel plate capacitance

- **T**wo components:

- What is  $C_{GC}$ ? ( $C_{GCS}$ ,  $C_{GCD}$ )

- What is C<sub>GCB</sub>?

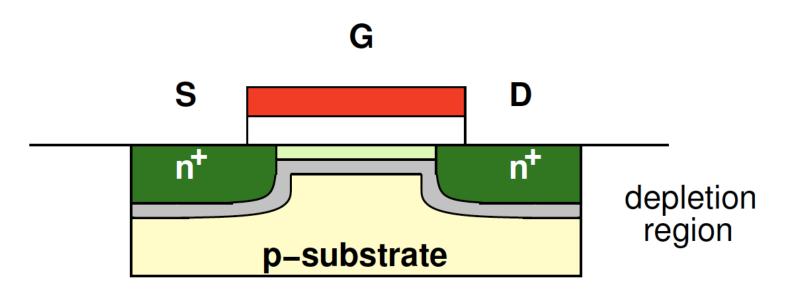

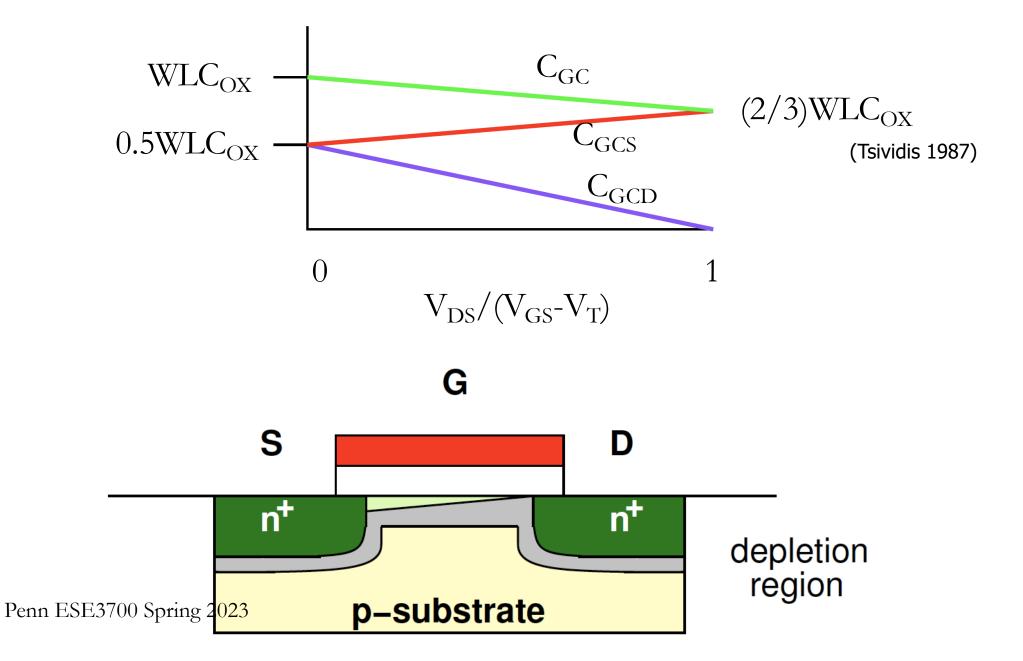

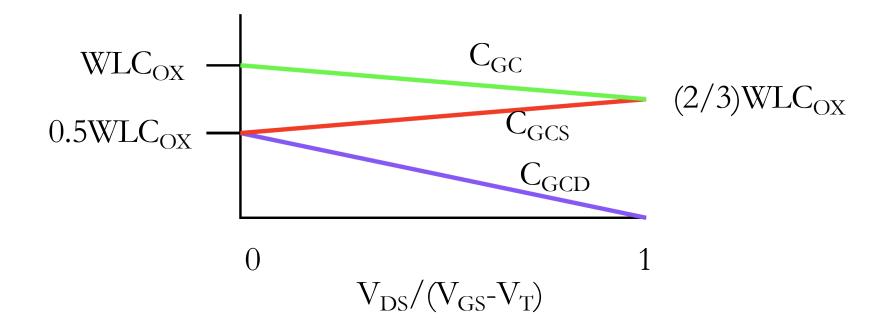

## Gate-to-Channel Capacitance

- Looks like parallel plate capacitance

- □ Two components: Case: Strong Inversion (small Vds)

- C<sub>GC</sub>

- C<sub>GCB</sub>

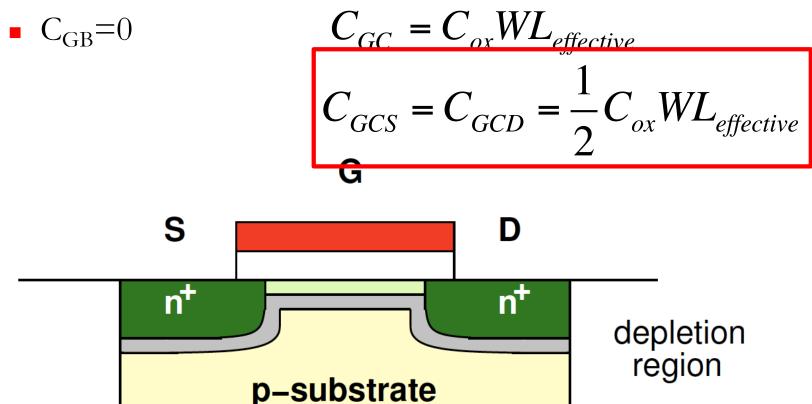

## Gate-to-Channel Capacitance

- Looks like parallel plate capacitance

- □ Two components: Case: Strong Inversion

•

$$C_{GC}$$

•  $C_{GCB}=0$   $C_{GC} = C_{ox}WL_{effective}$

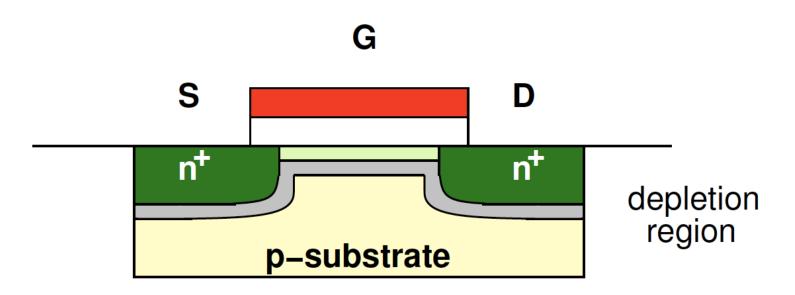

### Gate-to-Channel Capacitance

- Looks like parallel plate capacitance

- □ Two components: Case: Strong Inversion

- $C_{GC}$  Split evenly between S and D

□ Channel + Overlap

$$C_{GS} = C_{GCS} + C_{GSO}$$

□ Channel + Overlap

$$C_{GS} = C_{GCS} + C_{GSO}$$

$$C_{GS} = \frac{1}{2}C_{OX}W(L_{drawn} - L_{effective}) + \frac{1}{2}C_{OX}WL_{effective}$$

$$C_{GS} = \frac{1}{2}C_{OX}WL_{drawn}$$

G

$$C_{GS} = \frac{1}{2}C_{OX}WL_{drawn}$$

G

Penn ESE3700 Spring 2023

□ Channel + Overlap

$$C_{GD} = C_{GCD} + C_{GDO}$$

$$C_{GD} = \frac{1}{2}C_{OX}W(L_{drawn} - L_{effective}) + \frac{1}{2}C_{OX}WL_{effective}$$

$$C_{GD} = \frac{1}{2}C_{OX}WL_{drawn}$$

G

$$C_{GD} = \frac{1}{2}C_{OX}WL_{drawn}$$

G

Penn ESE3700 Spring 2023

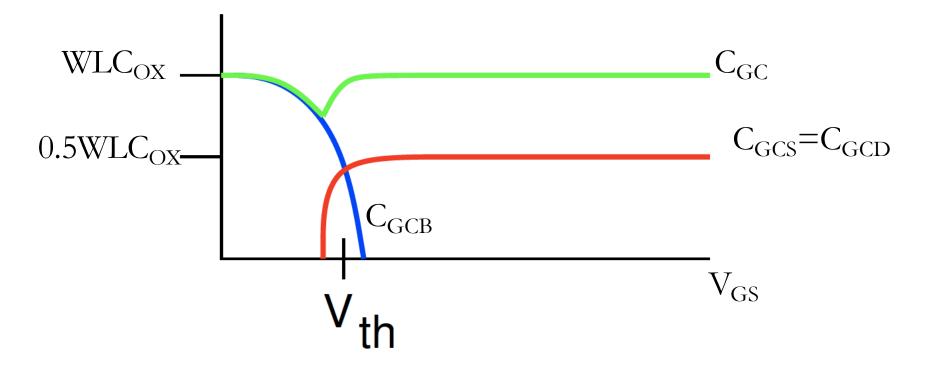

$$\Box V_{GS} = 0 \rightarrow C_{GC} = 0, C_{GCB} = WLC_{ox}$$

В

Penn ESE3700 Spring 2023

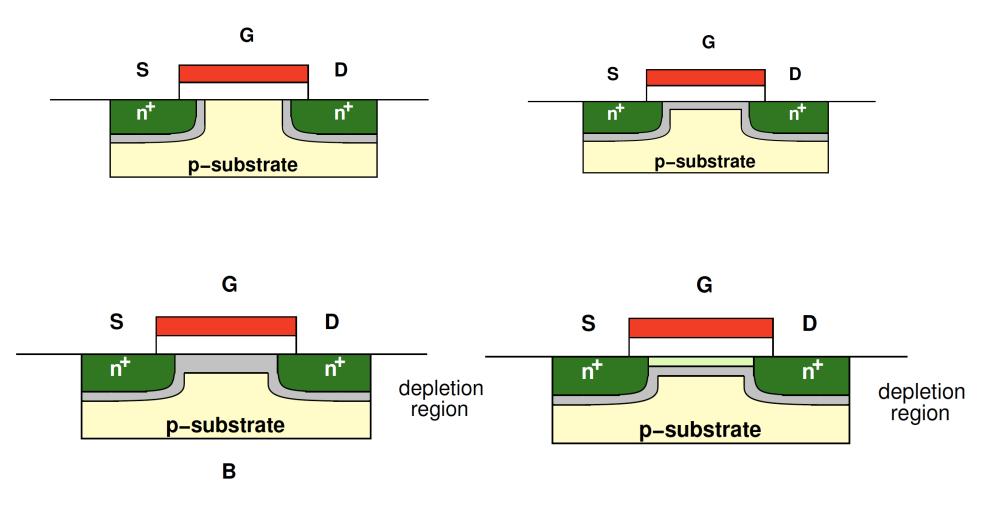

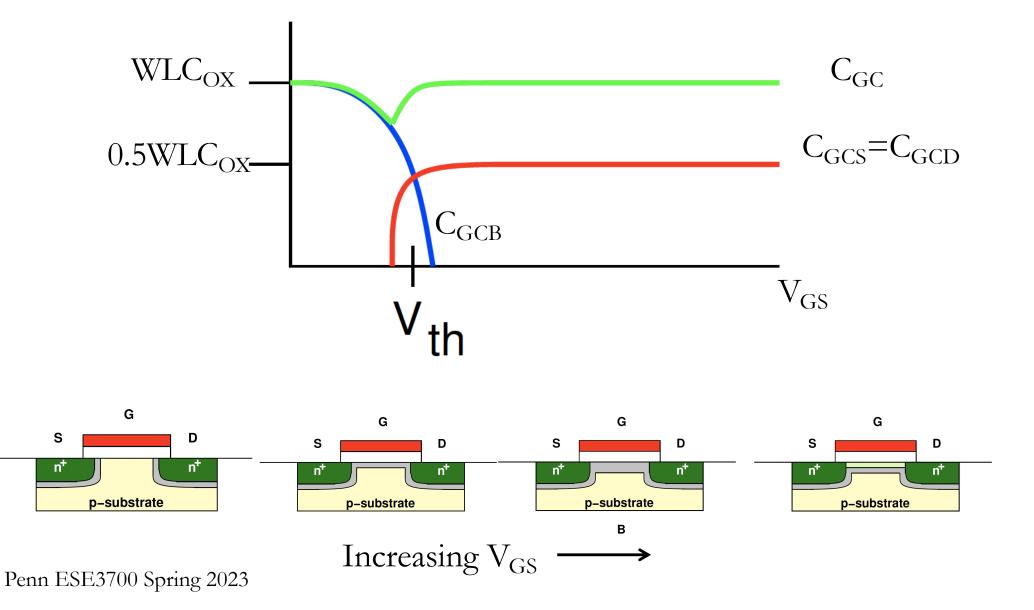

## Channel Evolution: Weak Inversion

#### $\square$ What happens to capacitance here as $V_{GS}$ increases?

Capacitor plate distance?

# Channel Evolution: Weak Inversion

- Capacitance is initially dominated by Gate-to-bulk capacitance (C<sub>GCS,D</sub>=0)

- Gate-to-bulk capacitance drops as V<sub>GS</sub> increases toward V<sub>th</sub>

Capacitance vs  $V_{GS}(V_{DS}=0)$

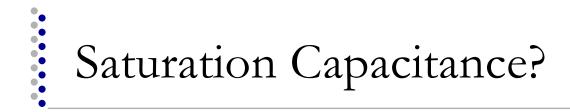

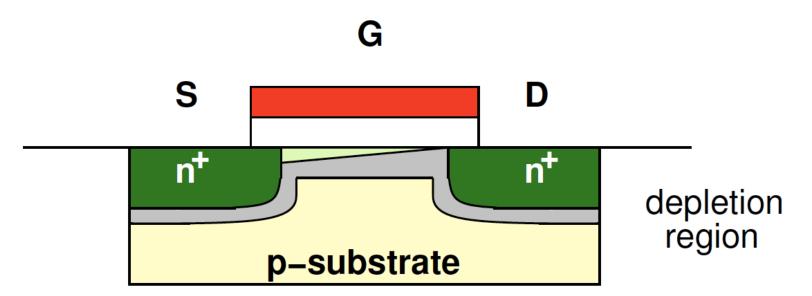

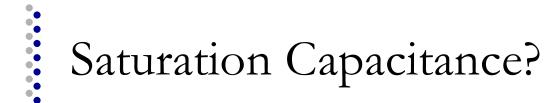

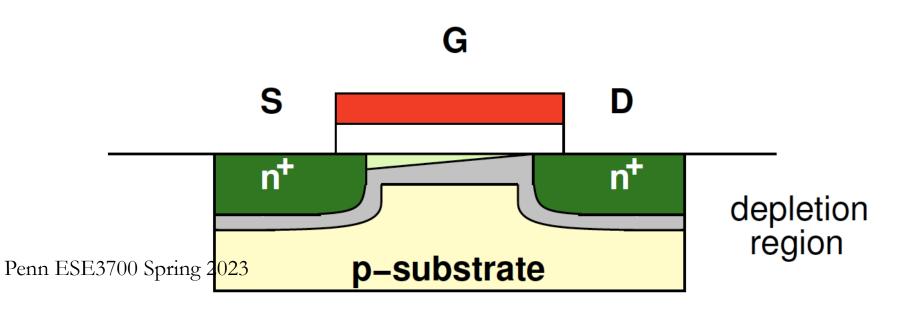

- □ Source end of channel in inversion

- Voltage at drain end of channel at or below threshold

- Capacitance shifts to source

- Total capacitance reduced

- $\Box C_{GS} = C_{GCS} + C_{GSO}$

- $\Box C_{GD} = C_{GCD} + C_{GDO}$

- $\Box C_{GB} = C_{GCB}$

- $\Box C_{SB} = C_{diff}$

- $\Box C_{DB} = C_{diff}$

| Operation<br>Region | C <sub>GCB</sub> | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub> | C <sub>G</sub> |

|---------------------|------------------|------------------|------------------|-----------------|----------------|

| Subthreshold        |                  |                  |                  |                 |                |

| Linear              |                  |                  |                  |                 |                |

| Saturation          |                  |                  |                  |                 |                |

First Order Capacitance Summary

| Operation<br>Region | C <sub>GCB</sub> | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub> | C <sub>G</sub> |

|---------------------|------------------|------------------|------------------|-----------------|----------------|

| Subthreshold        |                  |                  |                  |                 |                |

| Linear              | 0                | $C_{OX}WL/2$     | $C_{OX}WL/2$     |                 |                |

| Saturation          |                  |                  |                  |                 |                |

$$C_{GCS} = C_{GCD} = \frac{1}{2}C_{ox}WL_{effective}$$

First Order Capacitance Summary

| Operation<br>Region | C <sub>GCB</sub>   | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub> | C <sub>G</sub> |

|---------------------|--------------------|------------------|------------------|-----------------|----------------|

| Subthreshold        | C <sub>OX</sub> WL | 0                | 0                |                 |                |

| Linear              | 0                  | $C_{OX}WL/2$     | $C_{OX}WL/2$     |                 |                |

| Saturation          |                    |                  |                  |                 |                |

| Operation<br>Region | C <sub>GCB</sub>   | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub> | C <sub>G</sub> |

|---------------------|--------------------|------------------|------------------|-----------------|----------------|

| Subthreshold        | C <sub>OX</sub> WL | 0                | 0                |                 |                |

| Linear              | 0                  | $C_{OX}WL/2$     | $C_{OX}WL/2$     |                 |                |

| Saturation          | 0                  | $(2/3)C_{OX}WL$  | 0                |                 |                |

| Operation<br>Region | C <sub>GCB</sub>   | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub>    | C <sub>G</sub> |

|---------------------|--------------------|------------------|------------------|--------------------|----------------|

| Subthreshold        | C <sub>OX</sub> WL | 0                | 0                | C <sub>OX</sub> WL |                |

| Linear              | 0                  | $C_{OX}WL/2$     | $C_{OX}WL/2$     | C <sub>OX</sub> WL |                |

| Saturation          | 0                  | $(2/3)C_{OX}WL$  | 0                | $(2/3)C_{OX}WL$    |                |

| Operation<br>Region | C <sub>GCB</sub>   | C <sub>GCS</sub>        | C <sub>GCD</sub> | C <sub>GC</sub>         | C <sub>G</sub>                |

|---------------------|--------------------|-------------------------|------------------|-------------------------|-------------------------------|

| Subthreshold        | C <sub>OX</sub> WL | 0                       | 0                | C <sub>OX</sub> WL      | $C_{OX}WL+2C_{O}$             |

| Linear              | 0                  | $C_{OX}WL/2$            | $C_{OX}WL/2$     | C <sub>OX</sub> WL      | $C_{OX}WL+2C_{O}$             |

| Saturation          | 0                  | (2/3)C <sub>OX</sub> WL | 0                | (2/3)C <sub>OX</sub> WL | $(2/3)C_{OX}WL$<br>+ $2C_{O}$ |

$$C_{o} = \frac{1}{2}C_{ox}W(L_{drawn} - L_{effective}) = C_{GSO} = C_{GDO}$$

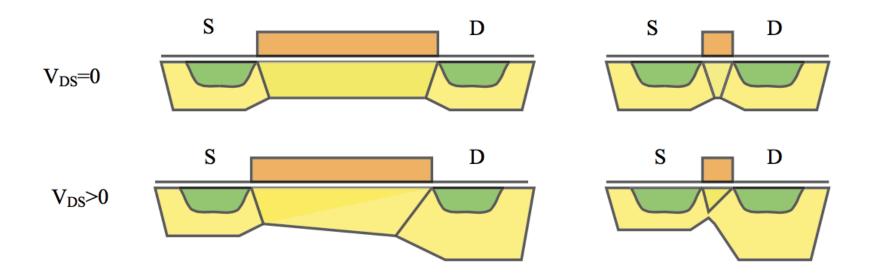

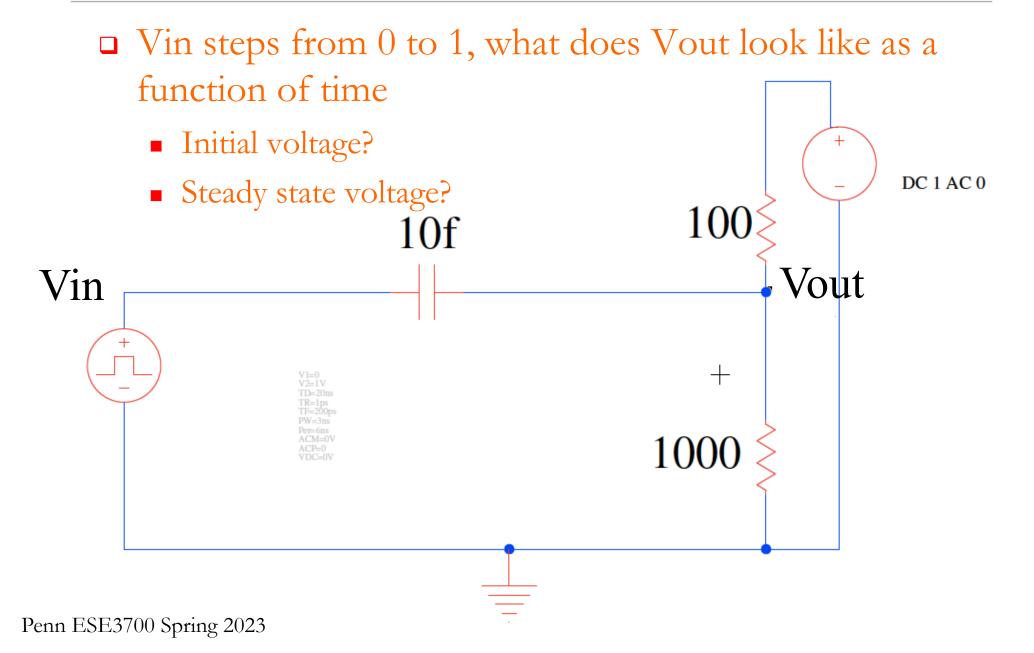

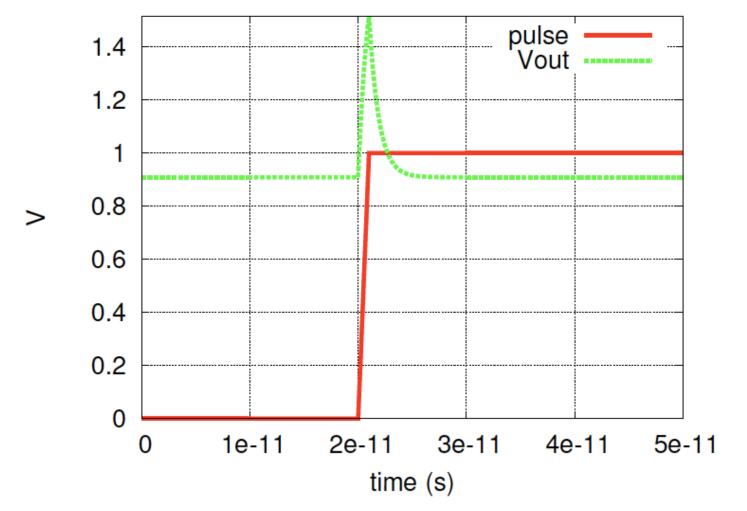

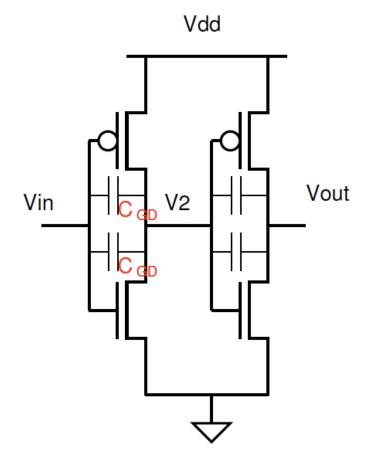

#### One Implication

#### Feedback Capacitance C<sub>gd</sub>

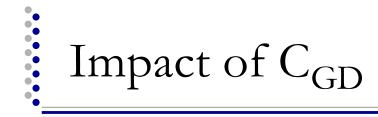

## Step Response? (Preclass 3)

$\Box$  What does  $C_{GD}$  do to the switching response here?

- V<sub>2</sub>

- V<sub>out</sub>

\*\*\* spice deck for cell flat\_inv{sch} from library test

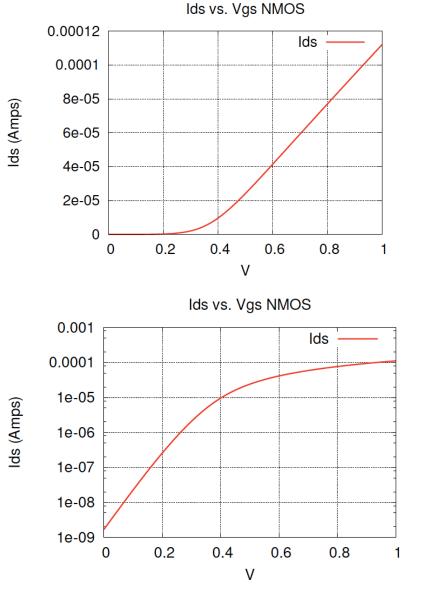

#### □ 3+ Regions of operation for MOSFET

- Subthreshold

- Linear

- Saturation

- Pinch Off

- Velocity Saturation, DIBL

- Short channel

Penn ESE3700 Spring 2023

- □ HW3 out now due 2/14 (Friday)

- Takes time! Learning curve for how to debug

- Don't forget the demo/video of SPICE workflow

- Prof. André DeHon (University of Pennsylvania)

- □ Prof. Tania Li (University of Pennsylvania)