## ESE 568: Mixed Signal Design and Modeling

Lec 5: September 17th, 2018 Basic 2-stage Opamp Design

Penn ESE 568 Fall 2018 - Khanna

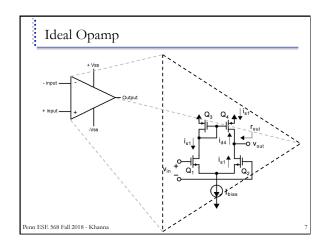

### Ideal Opamp

- □ The ideal opamp characterized by seven properties

- Knowledge of these properties is sufficient to design and analyze a large number of useful circuits

- □ Basic opamp properties

- Infinite open-loop voltage gain

- Infinite input impedance

- Zero output impedance

- Zero noise contribution

- Zero DC output offset

- Infinite bandwidth

- Differential inputs that stick together

- Zero input differential voltage

Penn ESE 568 Fall 2018 - Khanna

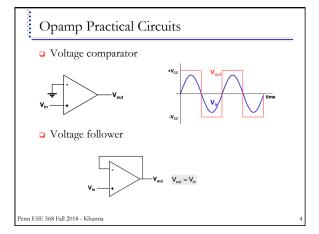

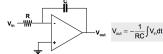

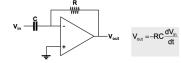

### Opamp Practical Circuits

□ Integrating amplifier

Differentiating amplifier

Penn ESE 568 Fall 2018 - Khanna

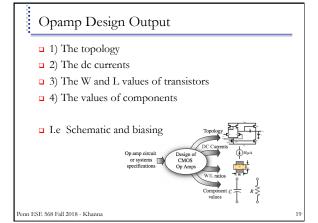

### Opamp Design

### Steps in Designing a CMOS Opamp

- 1) Choosing or creating the basic structure of the opamp

- This step results in a schematic showing the transistors and their interconnections

- This diagram does not change throughout the remainder of the design unless the specifications cannot be met, then a new or modified structure must be developed

- 2) Selection of the dc currents and transistor sizes

- a.k.a Biasing and sizing

- Most of the effort of design is in this category

- Simulators are used to aid the designer in this phase

Penn ESE 568 Fall 2018 - Khanna

### Steps in Designing a CMOS Opamp

- □ 3) Physical implementation of the design

- Layout of the transistors

- Floorplanning the connections, pin-outs, power supply buses and grounds

- Extraction of the physical parasitics and re-simulation

- Verification that the layout is a physical representation of the circuit

- 4) Fabrication

- □ 5) Measurement

- Verification of the specifications

- Modification of the design as necessary

- Make sure it's not necessary!

Penn ESE 568 Fall 2018 - Khanna

### Design Variables

- □ Boundary conditions (constraints):

- 1. Process specification (V<sub>T</sub>,  $\mu$ , C<sub>ox</sub>, etc.)

- 2. Supply voltage and range

- 3. Supply current and range

- 4. Operating temperature and range

Penn ESE 568 Fall 2018 - Khanna

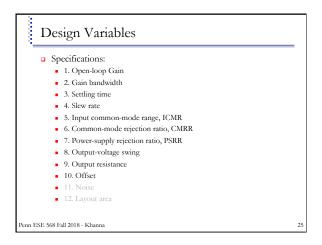

### Design Variables

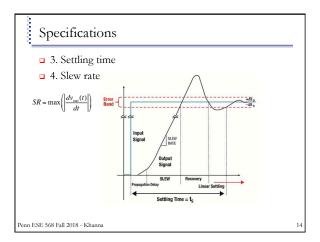

- Specifications:

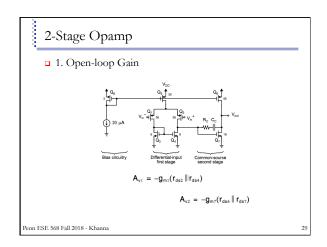

- 1. Open-loop Gain

- 2. Gain bandwidth

- 3. Settling time

- 4. Slew rate

- 5. Input common-mode range, ICMR

- 6. Common-mode rejection ratio, CMRR

- 7. Power-supply rejection ratio, PSRR

- 8. Output-voltage swing

- 9. Output resistance

- 10. Offset

- 11. Noise

- 12. Layout area

Penn ESE 568 Fall 2018 - Khanna

### Specifications

- □ 1. Open-loop Gain

- Typically an op-amp may have a maximal open-loop gain of around 10<sup>5</sup>

$$A_{OL} = \frac{V_{out}}{V_{in}^+ - V_{in}^-}$$

Penn ESE 568 Fall 2018 - Khanna

2

### Specifications

- □ 1. Open-loop Gain

- $\blacksquare$  Typically an op-amp may have a maximal open-loop gain of around  $10^5$

$$A_{OL} = \frac{V_{out}}{V_{in}^+ - V_{in}^-}$$

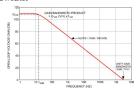

2. Gain bandwidth

### Specifications

Penn ESE 568 Fall 2018 - Khanna

- □ 5. Input common-mode range, ICMR

- The input common-mode range is the range of commonmode voltages over which the differential amplifier continues to sense and amplify the difference signal with the same gain.

Penn ESE 568 Fall 2018 - Khanna

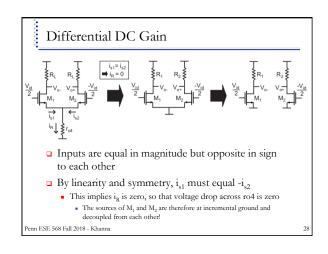

### Specifications

- □ 6. Common-mode rejection ratio, CMRR

- CMRR is a measure of how well the differential amplifier rejects the common-mode input voltage in favor of the differential-input voltage.

$$CMRR = \frac{a_{vd}}{a_{vc}}$$

□ 7. Power-supply rejection ratio, PSRR

$$PSRR_{+} = \frac{a_{vd}}{a}$$

$$PSRR_{-} = \frac{a_{vd}}{a}$$

Penn ESE 568 Fall 2018 - Khanna

### Specifications

- □ 8. Output-voltage swing

- Expected output swing

- 9. Output resistance

- Resistance seen into the output

- □ 10. Offset

- Output offset voltage (V<sub>OS</sub>(out))

- The output offset voltage is the voltage which appears at the output of the differential amplifier when the input terminals are connected together.

Penn ESE 568 Fall 2018 - Khanna

### Specifications

- □ 8. Output-voltage swing

- Expected output swing

- 9. Output resistance

- Resistance seen into the output

- □ 10. Offset

- Output offset voltage (V<sub>OS</sub>(out))

- The output offset voltage is the voltage which appears at the output of the differential amplifier when the input terminals are connected together.

- $\blacksquare$  Input referred offset voltage (V  $_{\rm OS}\!(in)$  = V  $_{\rm OS}\!)$

- The input referred offset voltage is equal to the output offset voltage divided by the differential voltage gain.

- $\quad V_{\rm OS} = V_{\rm OS}({\rm out})/A_{\rm VD}$

Penn ESE 568 Fall 2018 - Khanna

### Opamp Design Practical Advice

- □ 1) Decide upon a suitable topology

- The topology should be the one capable of meeting most of the specifications

- Try to avoid "inventing" a new topology but start with an existing topology

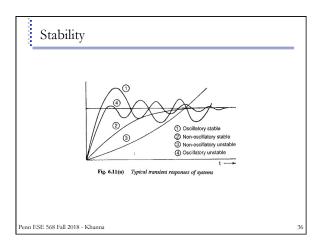

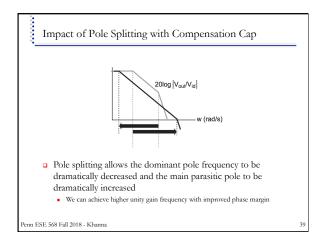

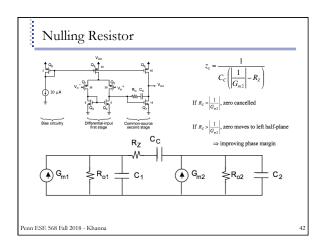

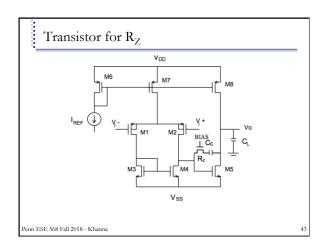

- 2) Determine the type of compensation needed to meet the specifications

- Consider the load and stability requirements

- Use some form of Miller compensation or a self-compensated approach

- 3) Design dc currents and device sizes for proper dc, ac, and transient performance

- This begins with hand calculations based upon approximate design conations.

- Compensation components are also sized in this step of the procedure.

- After each device is sized by hand, a circuit simulator is used to fine tune the design

Penn ESE 568 Fall 2018 - Khanna

20

### Opamp Design Practical Advice

- □ Two basic steps of design:

- 1) "First-cut" this step is to use hand calculations to propose a design that has potential of satisfying the specifications. Design robustness is developed in this step.

- 2) Optimization this step uses the computer to refine and optimize the design.

Penn ESE 568 Fall 2018 - Khanna

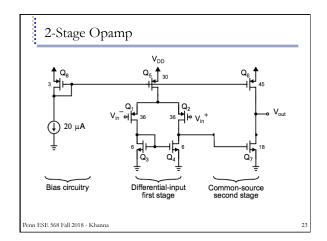

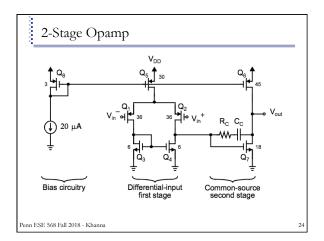

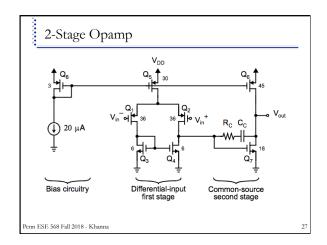

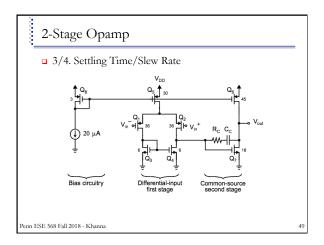

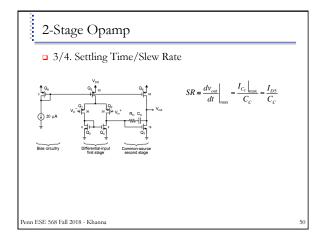

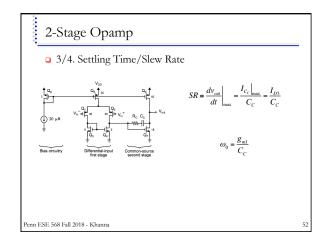

### Basic 2-stage Opamp

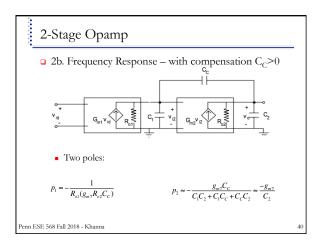

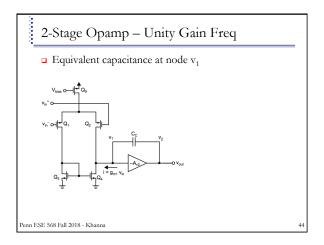

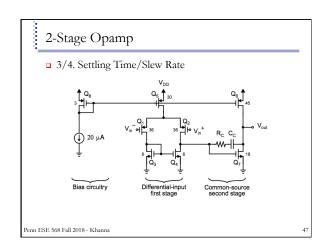

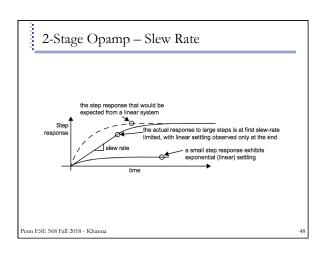

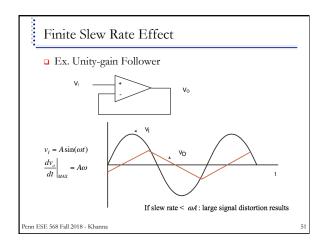

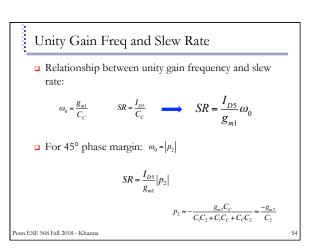

## Unity Gain Freq and Slew Rate Relationship between unity gain frequency and slew rate: $\omega_0 = \frac{g_{m1}}{C_C} \qquad SR = \frac{I_{D5}}{C_C} \qquad SR = \frac{I_{D5}}{g_{m1}} \omega_0$ Por 45° phase margin: $\omega_o = |p_2|$ $SR = \frac{I_{D5}}{g_{m1}} |p_2|$

Penn ESE 568 Fall 2018 - Khanna

# Design Variables Specifications: 1. Open-loop Gain 2. Gain bandwidth 3. Settling time 4. Slew rate 5. Input common-mode range, ICMR 6. Common-mode rejection ratio, CMRR 7. Power-supply rejection ratio, PSRR 8. Output-voltage swing 9. Output resistance 10. Offset 11. Noise 12. Layout area